Introducing Harock, Socionext’s 28nm 56Gb/s SerDes 2-lane test chip enabling 100G direct detect signaling while maintaining an ultra-low power profile and compact chip size.

Our collective appetite for data is nothing short of astounding – and it continues to grow. It isn’t just our casual smartphone addiction, either. Other trends are increasing data usage, including the popularity of streaming media, cloud computing, and the Internet of Things. In fact, we keep finding new and exciting ways to use more data all the time.

Service providers and data center operators, meanwhile, face the tremendous challenge of efficiently and cost-effectively keeping the high-speed data flowing. As our data cravings increase, so does their scramble to add capacity – along with all the associated equipment, facility, and power costs.

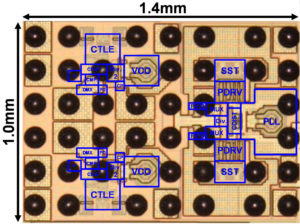

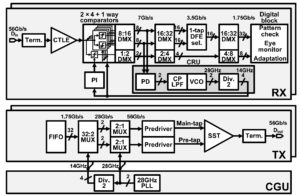

This is where the new Socionext 28nm 56Gb/s SerDes 2-lane device offers a much-needed solution. Our new test chip, codenamed “Harock,” enables ease of scalability to 100G direct detect signaling while maintaining an ultra-low power profile and compact die size. The Harock SerDes chip supports both NRZ and PAM4 signaling within an ultra-compact 1.4mm2 die size.

Harock is ideal for applications such as high-speed networking, optical transport, metro, data center, network intrusion prevention, and massive parallel CPU computing spaces.

Socionext Harock 28nm SerDes Test Chip

We designed Harock to be a unique and differentiated SerDes balancing performance, features and ultra-low power consumption.

Harock provides the outstanding transmitter performance required for today’s high-speed networking and lightwave applications. Total jitter is measured at close to 8.8ps @ BER 10-15 and random jitter is ~200-230fs.

Harock’s receiver passes jitter tolerance compliance for OIF’s CEI Ultra/Extra/Very Short Reaches (USR/XSR/VSR). The channel loss excluding the socket and package loss (estimated to be about 5dB) is 18.4dB @ 28.1GHz.

Meanwhile, Harock consumes less than ~250mW per lane.

We designed the Harock SerDes test chip with a rich set of features, including eye monitoring comparators, adaptive equalization (DFE), phase detectors, and clock recovery circuitry.

This impressive combination of high-performance, low power consumption and features make Harock a logical choice for companies who are migrating from existing 25Gb/s designs. Contact us to learn more.

See a Demo of Harock at DesignCon 2017

See a Demo of Harock at DesignCon 2017

Want to see a demo of Harock in person? The Harock SerDes test chip will be featured at the annual DesignCon at the Santa Clara Convention Center Booth# 1239 from Feb. 1- 2, 2017.

Please click here for more information.

Leave a Reply