“Fractional-N PLL” Ideal for New Generations of AI, 5G, IoT Applications

TOKYO and SANTA CLARA, Calif., and February 10, 2020 --- Scientists at Tokyo Institute of Technology (Tokyo Tech) and Socionext Inc. have designed the world’s smallest all-digital phase-locked loop (PLL), the two organizations announced today. All-digital PLLs enable new, high-performance system-on-chip (SoC) devices to serve emerging artificial intelligence, 5G cellular communications, and Internet-of-Things applications.

Reducing digital PLL size and improving performance is a significant step in enabling these next-generation applications, and creating a pathway to an SoC that can be fabricated in a small, 7-nm form factor, and in the coming generation of 5-nm technology.

Easy to Adopt Fractional-N PLL for Miniaturized ICs

As a core building block of SoC devices, the PLL synchronizes with the frequency of a reference oscillation and outputs a signal with the same or higher frequency, generating ‘clocking signals ‘ to provide a precise timing reference for the harmonious operation of digital devices. Traditional PLLs require analog components that are bulky and difficult to scale down; digital PLLs eliminate those restructions.

Scientists at Tokyo Tech and Socionext Inc., led by Prof. Kenichi Okada, implemented a ‘synthesizable’ fractional-N PLL, which requires only digital logic gates, making it easy to adopt in conventional miniaturized integrated circuits.

Okada and the team used several techniques to minimize the required area of the synthesizable PLLs, including power consumption and jitter, which is defined as the unwanted time fluctuation when transmitting digital signals. To decrease the required footprint, the design team employed a compact ring oscillator that can be easily scaled down. To suppress jitter, they reduced the phase noise (random fluctuations in a signal) of the ring oscillator, using ‘injection locking’, which is the process of synchronizing an oscillator with an external signal whose frequency, or multiple of it, is close to that of the oscillator. This was achieved over a wide range of frequencies. The lower phase noise, in turn, enables reduced power consumption.

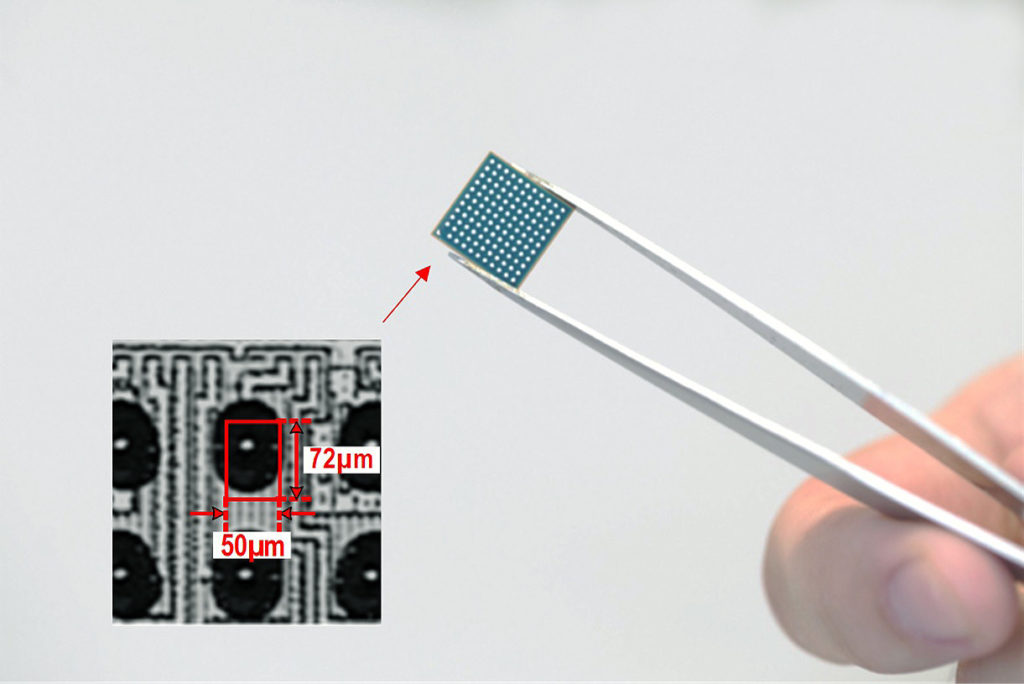

According to Professor Okada, the design of the synthesizable PLL is superior to all other current state-of-the-art PLLs because it achieves the best jitter performance with the lowest power consumption and the smallest area (see Figure 1). “The core area is 0.0036 mm2, and the whole PLL is implemented as one layout with a single power supply,” said Okada. Also, it can be built using standard digital design tools allowing for rapid, low-effort, and low-cost production, making it commercially viable.

The entire all-digital PLL fits in a 50 × 72 µm2 region, making it the smallest PLL to date.

The synthesizable PLL can be easily integrated into the design of all-digital SoCs, making it valuable for developing the next-generation 5-nm semiconductor technology, an important factor for 5G, artificial intelligence, Internet of Things and other applications where high performance and low power consumption are critical.

Potential of Synthesizable Circuits

The contributions of this research go beyond these possibilities. “Our work demonstrates the potential of synthesizable circuits,” said Okada. “With the design methodology employed here, other building blocks of SoCs, such as data converters, power management circuits, and wireless transceivers, could be made synthesizable as well. This greatly boosts design productivity and can reduce design efforts.”

Tokyo Tech and Socionext will continue their collaboration in this field to advance the miniaturization of electronic devices, enabling new technologies.

The research work was conducted in cooperation with TeraPixel Technologies Inc.

Reference

| Authors: | Bangan Liu1, Yuncheng Zhang1, Junjun Qiu1, Hongye Huang1, Zheng Sun1, Dingxin Xu1, Haosheng Zhang1, Yun Wang1, Jian Pang1, Zheng Li1, Xi Fu1, Atsushi Shirane1, Hitoshi Kurosu2, Yoshinori Nakane2, Shunichiro Masaki2, Kenichi Okada1 |

| Title of original paper: | A Fully-Synthesizable Fractional-N Injection-Locked PLL for Digital Clocking with Triangle/Sawtooth Spread-Spectrum Modulation Capability in 5 nm CMOS |

| Journal: | IEEE Solid-State Circuits Letters |

| DOI: | 10.1109/LSSC.2020.2967744 |

| Affiliations: | 1. Tokyo Institute of Technology, Tokyo, Japan

2. Socionext Inc., Yokohama, Japan |

*Corresponding author’s email: [email protected]

Contact

Emiko Kawaguchi

Public Relations Section,

Tokyo Institute of Technology

[email protected]

+81-3-5734-2975

Corporate Planning Office

Socionext Inc.

http://www.socionext.com/en/contact

+81-45-568-1006

About Tokyo Institute of Technology

Tokyo Tech stands at the forefront of research and higher education as the leading university for science and technology in Japan. Tokyo Tech researchers excel in fields ranging from materials science to biology, computer science, and physics. Founded in 1881, Tokyo Tech hosts over 10,000 undergraduate and graduate students per year, who develop into scientific leaders and some of the most sought-after engineers in industry. Embodying the Japanese philosophy of “monotsukuri,” meaning “technical ingenuity and innovation,” the Tokyo Tech community strives to contribute to society through high-impact research. www.titech.ac.jp/english/

About Socionext America Inc.

Socionext America Inc. (SNA) is the US branch of Socionext Inc., one of the world’s leading fabless SoC suppliers. Headquartered in Milpitas, California, the company provides leading-edge technologies and offers a wide range of standard and customizable SoC solutions. Socionext America meets customers' requirements with quality semiconductor products based on extensive and differentiated IPs, proven design methodologies, and state-of-the-art implementation expertise, with full support.

For product information, visit our website, e-mail [email protected] or call 1-844-868-1795. For company news and updates, connect with us on LinkedIn, YouTube, Facebook and Twitter.

About Socionext Inc.

Socionext Inc. is a global SoC (System-on-Chip) supplier and a pioneer of a unique “Solution SoC” business model through decades of industry experience and expertise. Socionext contributes to global innovation in advanced technologies including automotive, data center, networking, and smart devices. As a trusted silicon partner, Socionext delivers superior features, performance, and quality that differentiate its customers’ products and services from their competition.

Socionext Inc. is headquartered in Yokohama, and has offices in Japan, Asia, United States and Europe to lead its development and sales activities. For more information, visit https://www.socionext.com/en/.

All company or product names mentioned herein are trademarks or registered trademarks of their respective owners. Information provided in this press release is accurate at time of publication and is subject to change without advance notice.