Socionext provides its proprietary subsystems for specific functions. These versatile subsystems provide the flexibility customers need to differentiate their products. Both the hardware and the Software Development Kit (SDK) are available.

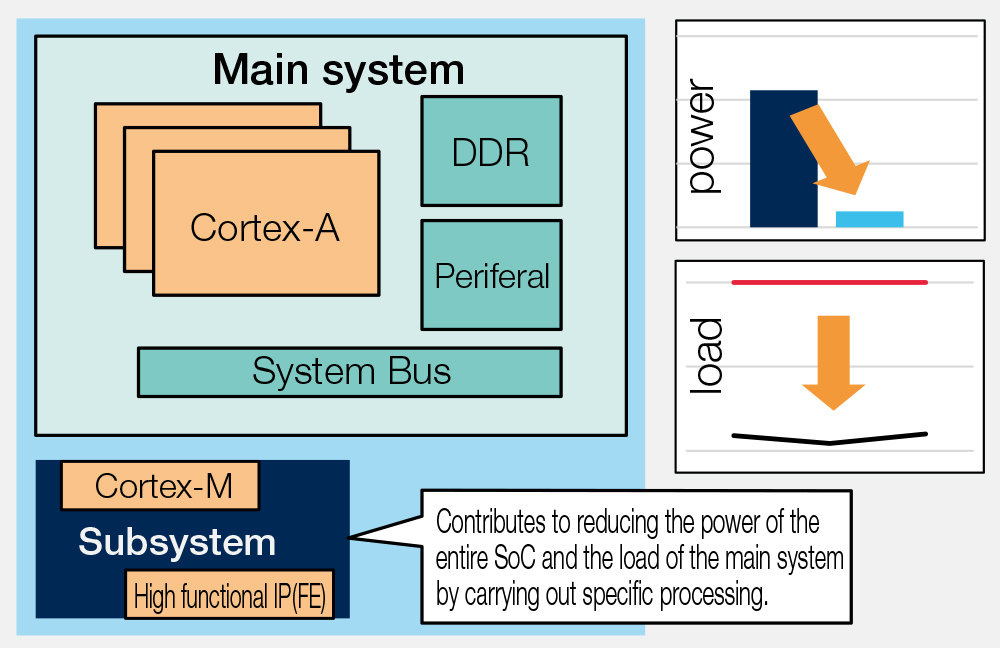

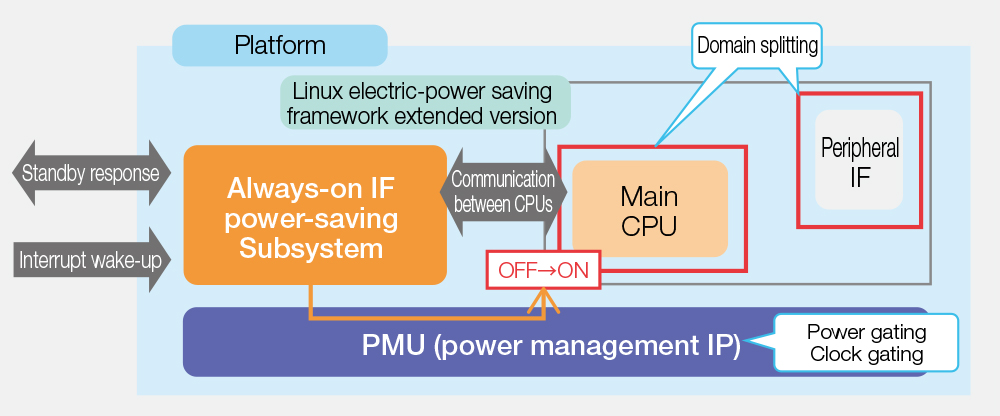

Power-saving Subsystem

Today SoCs are getting more functional and highly integrated, yet need to be more power efficient. . Our power-saving subsystem satisfies these two otherwise conflicting goals: improved performance and lower power consumption.

The power-saving subsystem integrates the following electric-power-saving features to lower power consumption.

- Network standby response such as Ethernet and USB

- Centralized management of power gating and clock gating

- Linkage with the electric-power-saving function of the OS

- Linkage with the power monitor

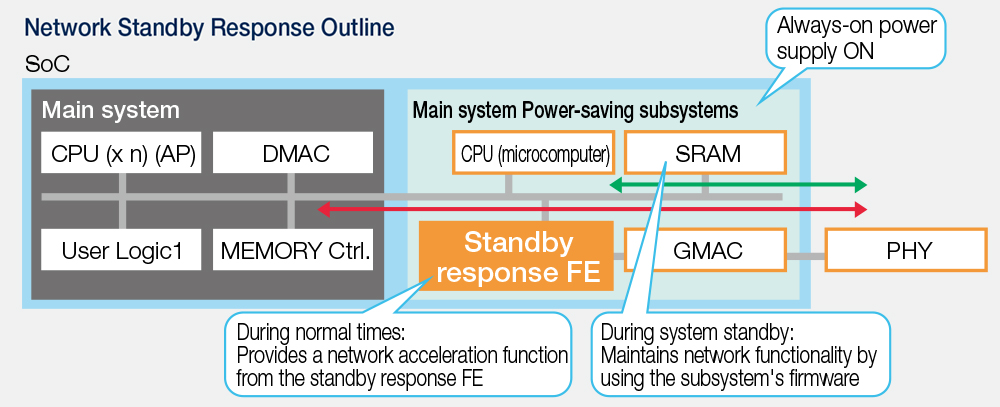

Network-Standby-Response Subsystem

The network-standby-response subsystem reduces the power consumption of the SoC when it is not in use. The subsystem offloads the process of maintaining a network connection to a separate power source, making it possible to maintain the response to the network while reducing power consumption.

While in stand-by, the network standby response subsystem and the firmware on the SRAM within the subsystem execute the network-filtering processes and packet processes.

Features

- High-speed execution of each process with the hardware assist.

(Checksum process, TCP/IP segmentation process, etc.) - Offloading function enabling the load reduction at the main-system-side CPU

- Improved communication quality by the packet-loss-prevention function

- Network-standby-response function with the small-scale circuit

- Platform (OS) independent SDK

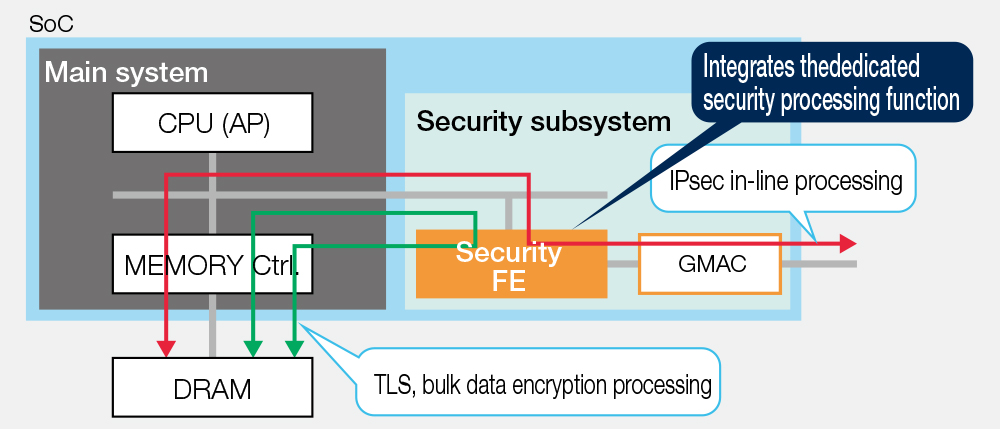

Security Subsystem

As the use of the Internet and cloud services spreads, security becomes even more important. Confidential information stored in the network connected equipment must be protected, and unauthorized access or illegal operation must be prevented. That requires sophisticated security functions. However, functions such as encryption calculations and authentication computing impose a heavy load on a CPU. Therefore, applying such security functions to various units has not been easy. To address this problem, Socionext provides subsystems most suitable for the application of these security functions.

Using the subsystem based on the compact controller (micro engine) enables various functions to be offloaded. This includes complex processes such as TLS and IPsec, network processes, general-purpose encryption, and authentication processes. As high-load processes are executed by the dedicated hardware, the CPU load in the main system can be greatly reduced.

Features

- Support of various encryption and authentication algorithms

(e.g., DES/3DES, AES, ARC4, MD5, SHA1/256/512) - Various hardware offloading and acceleration functions

(e.g., TCP/IP checksum, TCP segmentation, IPsec frame, TLS record) - Gigabit Ether MAC (optional)

- Acceleration of exponentiation, multiplication, division and remainder calculation required in RSA, by public key encryption calculation acceleration macro (F_PKA) (optional)

- Public key encryption calculation acceleration macro (F_PKA) also available as a standalone macro

- Platform (OS) independent SDK

Support Algorithm

| IPsec | TLS | Generic | ||

| Encryption | DES-ECB / 3DES-ECB | |||

| DES-CBC / 3DES-CBC | ||||

| AES-ECB | ||||

| AES-CBC | ||||

| AES-CTR | - | |||

| ARC4 | ||||

| AES-XTS | ||||

| AES-GCM | - | |||

| Authentication | MD5 | (HMAC) |

(HMAC) |

|

| SHA1 / SHA256 | (HMAC) |

(HMAC) |

||

| SHA512 | ||||

| AES-XCBCMAC- 96 | - | |||

Key Length:

*1: 128/192/256 bit | *2: 128/256 bit | *3: 128 bit

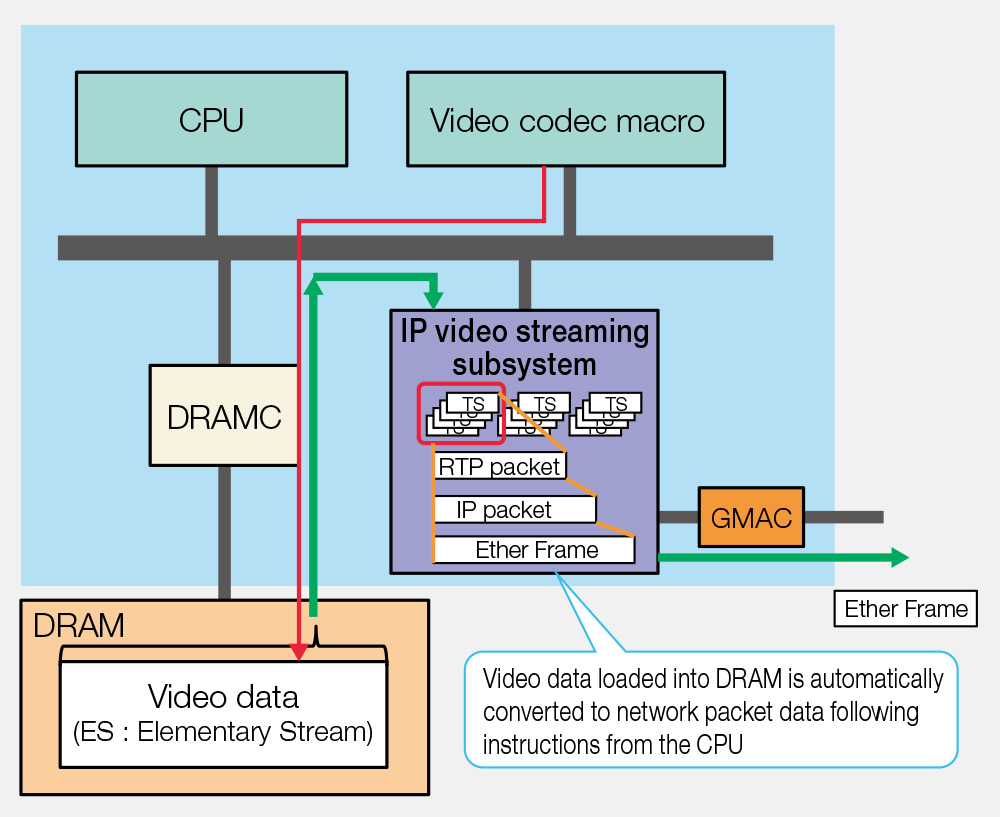

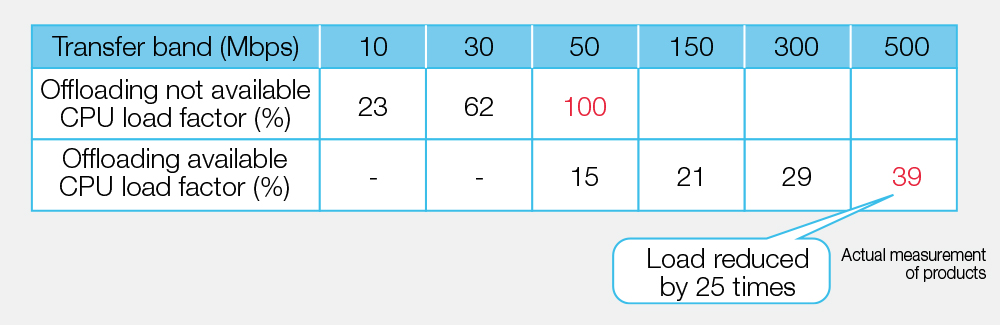

IP Video Streaming Subsystem

With the spread of the Internet, the need for video streaming is growing. Typical examples are media servers and network monitoring cameras. In such target areas, this subsystem carries out IP packetization of video data, significantly reducing the processing load of the main system.

Using the Flexware Engine™ as the key part, this subsystem encapsulates video and audio data into an IP packet and encapsulates the IP packet into an Ethernet frame. The following series of processes are performed in the high performance subsystem upon the video data.

Features

- Support for RTP/UDP offloading

[Supported formats]

- ES over RTP : Video(H.264), Audio(G.771, AAC)

- JPEG over RTP

- TS over RTP

- Metadata over RTP - Support for Max.32 streams

- Integration with security (encryption) functionality

Video Codec Subsystem

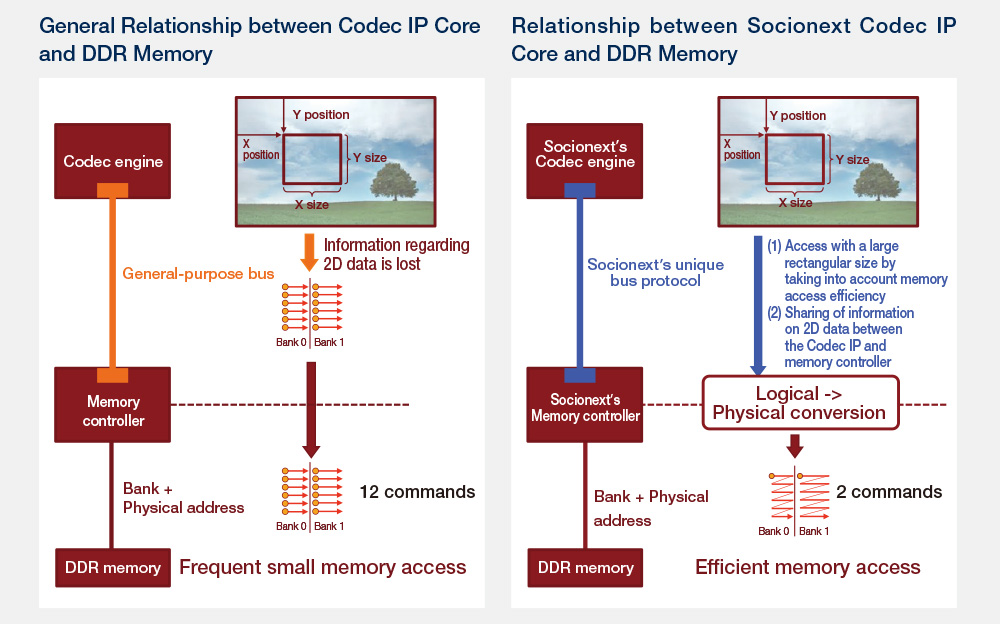

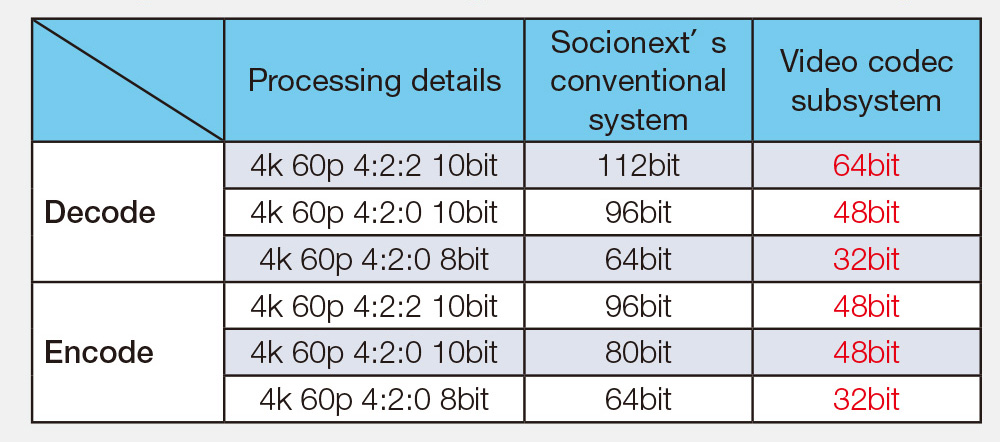

Due to an imbalance between the advance of DDR memory to the ultra-high speed generation along with an increase in the burst length and access by video codec processes handling small size rectangular image data to the DDR, a reduction in the efficiency of using the DDR memory band width has become an issue. This subsystem enables high efficiency video codec processing that can save the band width using Socionext’s unique technology.

We have developed our unique bus protocol methodology that can improve memory access efficiency in the codec process without being significantly affected by advances in DDR. Tightly coupling our codec engine and our memory controller with the methodology enables the memory controller to efficiently access DRAM by taking into account a physical memory map based on the 2D information on image data accessed by the codec engine, reducing the required memory band width significantly.

Features

Achieves HEVC codec processing with a smaller bus width (bit) as listed below.

Video Codec Subsystem

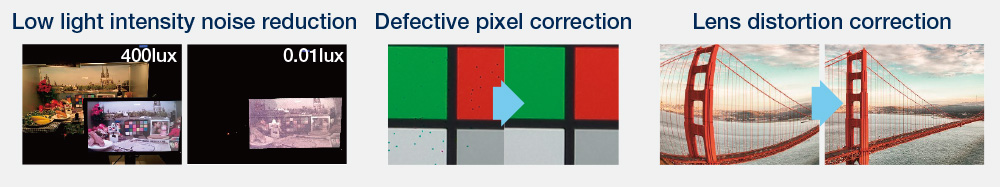

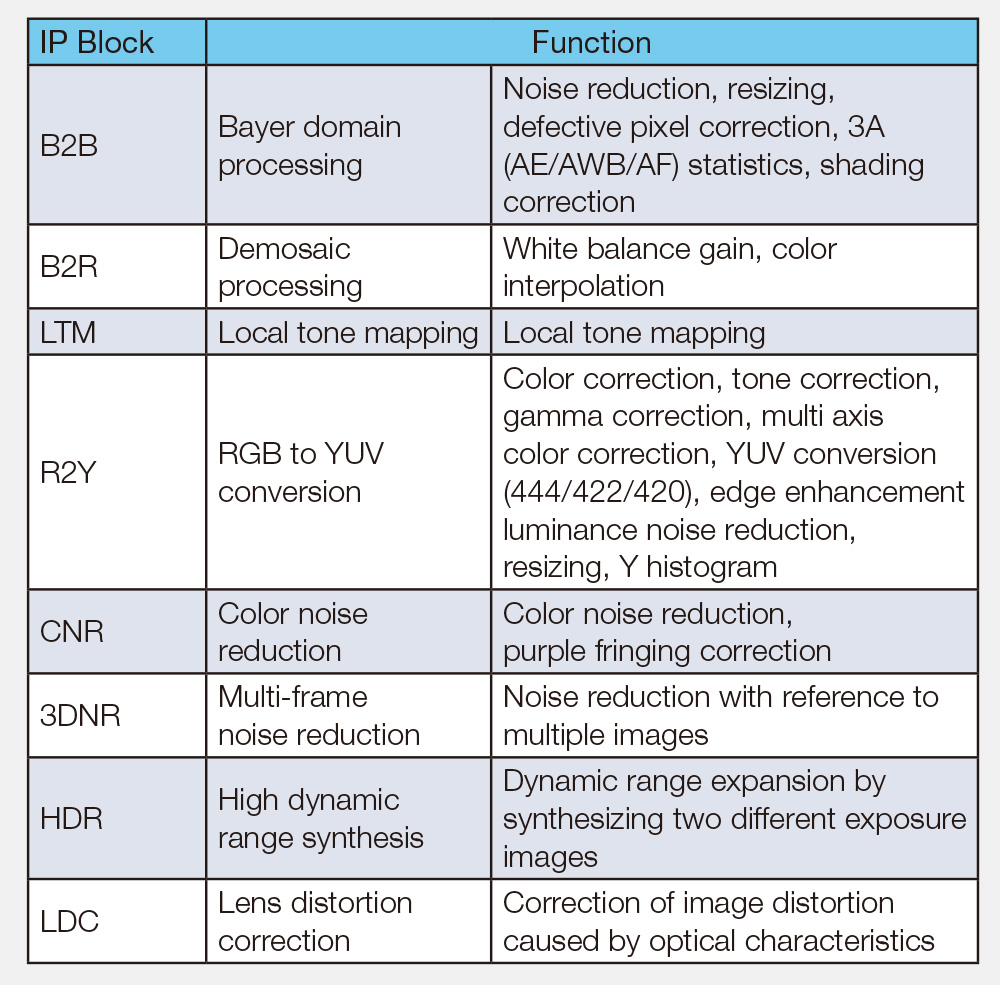

Under the current circumstances where camera solutions continue to advance, it is extremely difficult to keep providing new functionality and offering differentiating features every year. We have created IP for the image macro part of our image signal processor (Milbeaut®) with a track record of 18 years and provide it as a high-resolution, high performance subsystem.

By creating IP for an image macro for each functional block, it is possible to build a flexible platform. Each IP has the AXI interface so SoC integration is easy.

Features

- High-performance 4Kp60 600Mpix/sec (ex TSMC 28nm HPC+)

- API for effectively using image macros is provided.

- An image adjustment simulator is provided to emphasize the individuality of images.