Socionext provides interface macros that are optimized for various applications to help its customers develop advanced SoCs.

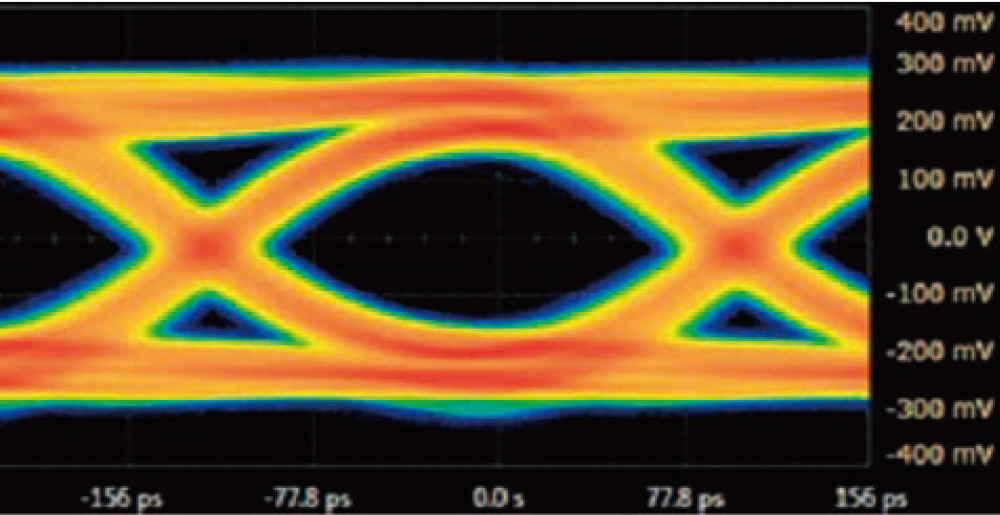

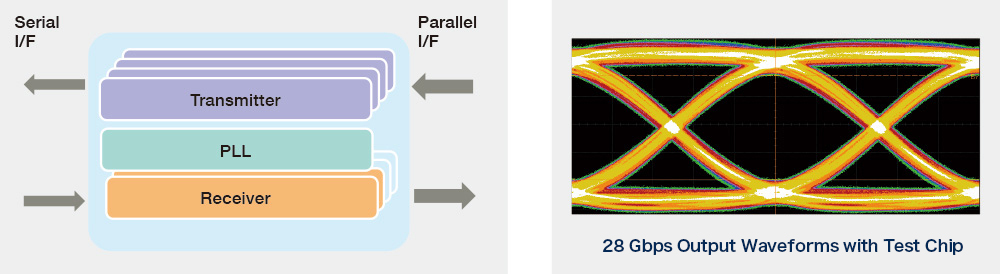

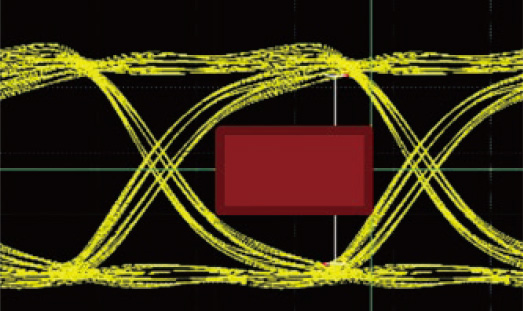

10G-28Gbps SerDes Interface

With a transmission performance of 10Gbps-28Gbps per channel and configuration comprising of multiple channels, our high-performance SerDes macro is appropriate for 100G/200G/400G optical networks or 100G Ethernet systems.

The built-in low-jitter, high-performance PLL enables robust transmission up to 28Gbps per channel.

The interface also supports various standards including OIF-CEI-11G-SR, OIF-CEI-28G-SR, OIF-CEI-28G-VSR, IEEE802.3ba CAUI4, and XFI.

Features:

- ×1, ×4 lane configuration.

- Comprising of Transmitter/Receiver/PLL and capable of bidirectional communication with 1 macro.

- Up to 112.8Gps per macro (for unidirectional, ×4 configuration).

- Power-down control on each lane supported.

- Power-down control for the entire macro supported.

- Implementing Clock-Data recovery for each Receiver lane.

- Transmitter Equalization supported.

- Receiver Equalization supported.

- Built-in termination resistor in Transmitter/Receiver.

- Organic flip chip package.

(0.8mm/1.0mm Ball Pitch, HDBU & SHDBU Package)

10G-28Gbps SerDes Interface

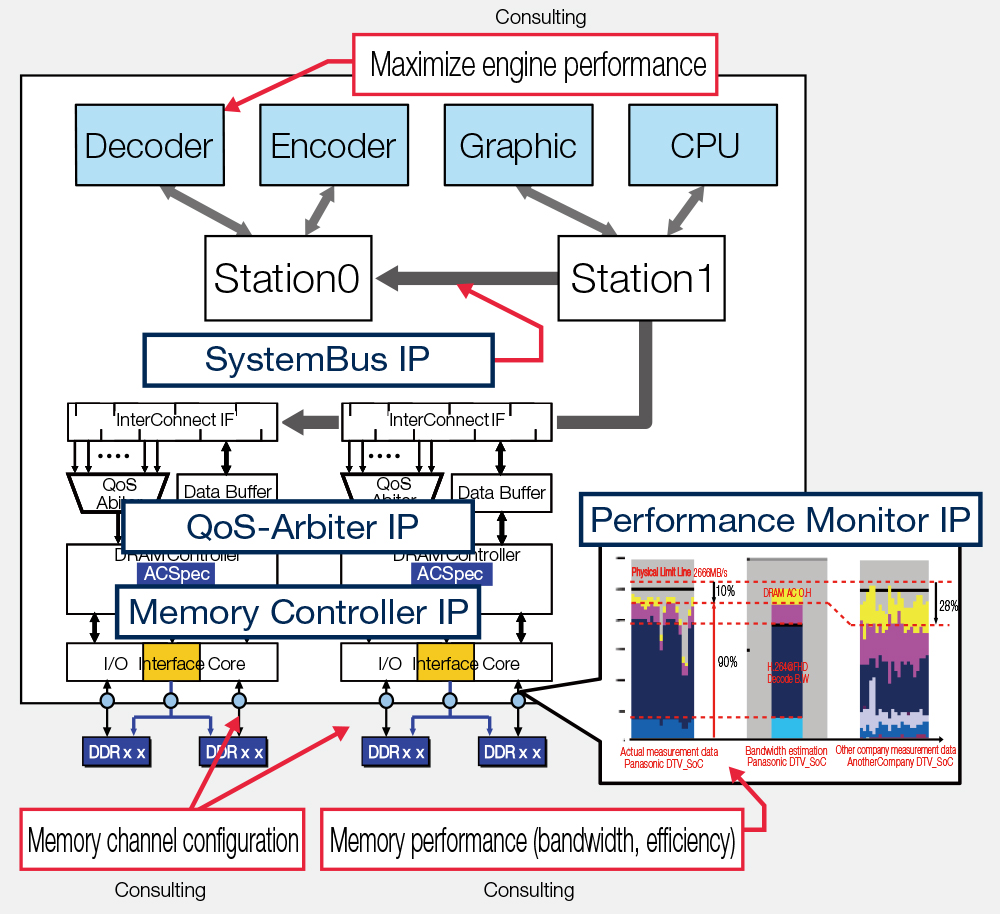

Memory Controllers

Socionext provides various memory solutions for system optimization. We also offer consulting services on memory systems including memory channels and the system bus to maximize SoC performance.

Memory controller IP

- Controller for maximizing high DRAM utilization.

QoS-Arbiter IP

- High performance QoS-Arbiter featuring multiple functions.

Bus IP

- Original low power consumption bus with high layout flexibility.

Monitor IP

- Visualizes memory system performance in real-time.

- Monitors performance (bandwidth, latency) and provides an environment for tuning parameters.

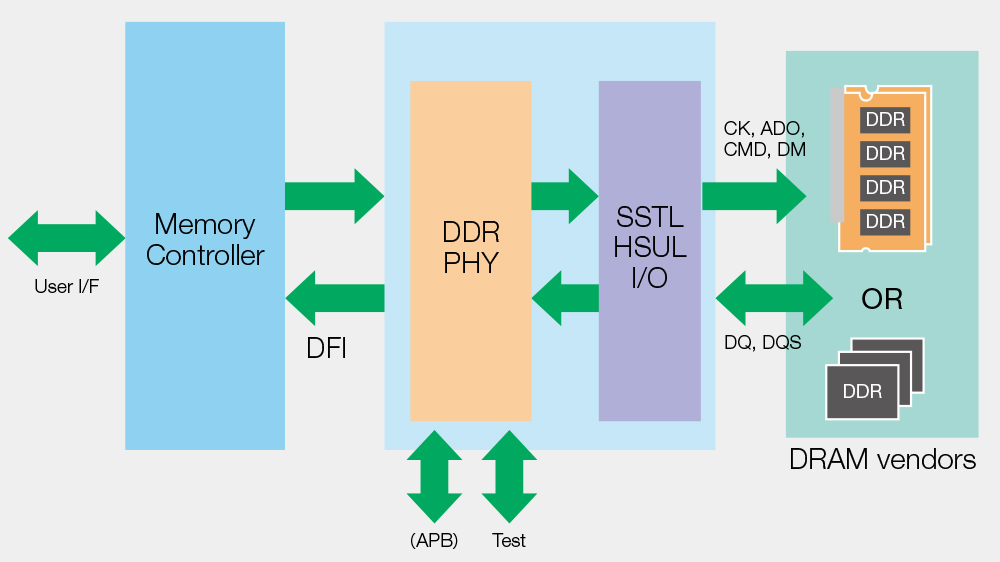

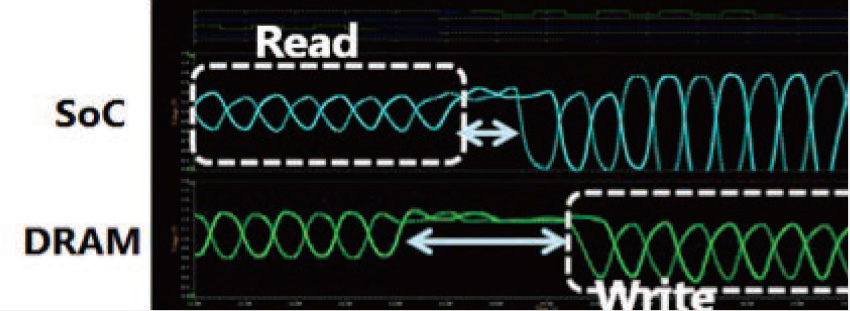

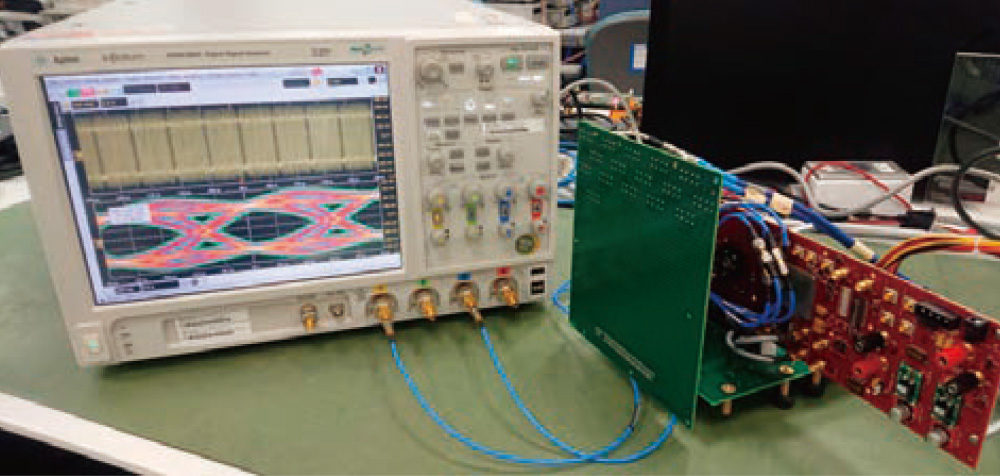

DDR Interface

Our various DDR interface macros range from low and middle speed, forwarding bandwidth to high-speed, forwarding bandwidth or low power, with our various process technologies. Moreover, we support custom SoC development by LSI package board co-design.

DDR Interface Macros

- High-speed/high-bandwidth DDR3/DDR4

- Low-power LPDDR4X/4/3/2DDR3L

- DFI compliant (all macro)

- Compatible with many different DRAM configurations and PKG options, such as Fly-by or PoP, by PHY function (training function).

DDR Interface Design Support (LSI-Package-Board co-design)

- Timing verification: Verifies timing of all DDR-IF systems including delays between LSI I/O and DRAM

- Power Integrity: Optimizes the parasitic inductance, resonant frequency, and power supply (PKG, PCB) impedance as the power supply impedance design

- Signal Integrity: Optimizes the driver strength, terminator resistance, and interconnect topology

PCI Express Interface

The significant improvement of CPU processing capability and the increasing need for large-size data transmission make it difficult to achieve the expected architecture performance with the existing bus. PCI Express technology is a high-speed interface that enables data transmission of several hundreds of megabytes. Our PCI Express macro is applicable to maximum of 8 GT/s (Gen3). It has passed the PCI Express standard compliance test sponsored by PCI-SIG, and mutual connectivity and reliability with various types of PCI Express interface have been confirmed.

PCI Express LINK Macro

- Compliant with the standard regulation PCI Express Base Specification rev. 3.0

- Supports lane numbers ×1/ ×4/ ×8.

- DualMode (RootComplex/Endpoint selectable)

- AMBA3 I/F selectable for user interface.

- Integrated DMAC

PCI Express PHY Macro

- Maximum bit transmission rate 64GT/s

- Warrants high-speed signal transmission by the de-emphasis function

- LINK macro interface compliant with the standard regulation PIPE3/PIPE4.

MIPI LLI Interface

This high-speed interface is used to build a camera and display system by combining high-speed, high resolution CMOS image sensors. This interface provides a solution for highly expressive images.

MIPI D-PHY TX Macro

- 4-data lane + 1-clock lane configuration

- Transmission speed: 80 Mbps to 4.5 Gbps per lane

- Equalization function

- The world’s smallest footprint

- D-PHY2.0 compliant