# Improve the value of your products with

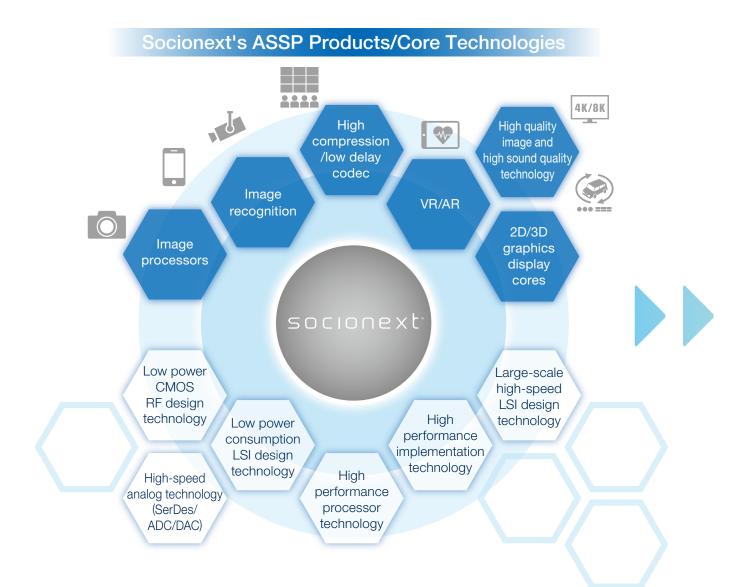

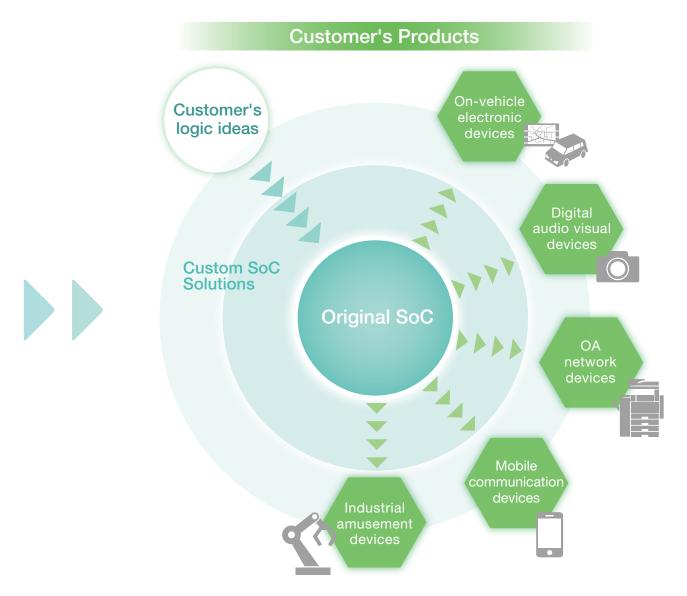

We have a full line-up of application-specific standard products (ASSPs) geared toward the consumer, industrial, and automotive markets. We also provide development services for custom SoCs according to your unique specifications. Our custom SoC development ranges flexibly from development based on our ASSP assets to fully customized development, meeting your needs with regard to performance, electric power, and downsizing.

50

0

Ρ

L.

# Socionext's system LSI solutions.

## CONTENTS

| 1 | Custom SoC Solution 1                           |

|---|-------------------------------------------------|

| 2 | Development Support Service (Design Express™) 8 |

| 3 | Subsystem Service16                             |

| 4 | IP Macro Service25                              |

| 5 | Design Technology32                             |

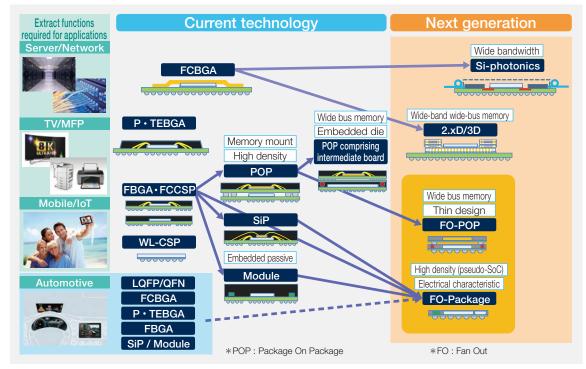

| 6 | Manufacturing Technology Package                |

# **Custom SoC Solution**

## System LSI solutions that offer new value

Our custom SoCs achieve downsizing, power saving, and cost reduction by integrating functional components. By incorporating value (functionality) that has yet to be commercialized, we help differentiate your products. With our wealth of IPs and subsystems, we fully utilize our design services for development support and our leading SoC design technology to optimize our products to your specification requirements, and provide high-quality and optimized custom SoCs.

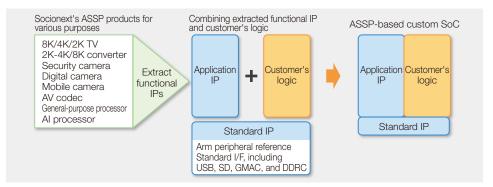

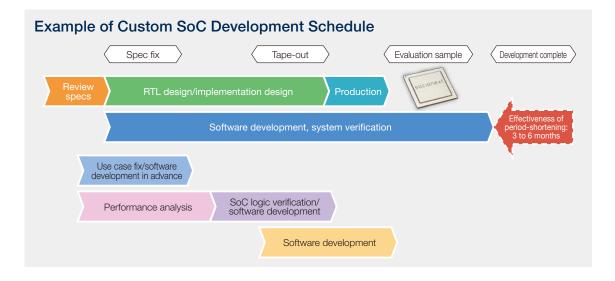

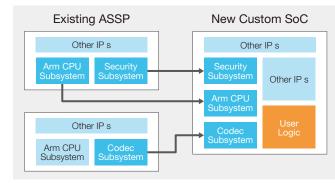

## Solution for Development Based on Existing Products

Developing a custom SoC based on an ASSP with a proven track record in the market not only makes it easy to design the components surrounding the CPU and the subsystems. It also has the advantage of easier development and evaluation because related software is also already provided.

## **Benefits of ASSP-based Development**

Where a product is designed based on our ASSP product, the development period will be six months shorter than that by conventional design. We achieve this rapid time-to-market by shortening the hardware design period for SoC development and by developing software in advance.

- Delivery time of sample SoC : Six months ahead of schedule

- · Advance development of software : Eight months ahead of schedule

- Product shipping : Six months ahead of schedule

| Full Custom Development                                                   |                                                   |  |  |  |  |

|---------------------------------------------------------------------------|---------------------------------------------------|--|--|--|--|

| HW Specification   Logic design/verification                              | n ES manufacturing                                |  |  |  |  |

| SW Specification Shortening period for CPU peripheral design/verification | Six month earlier for ES out Software development |  |  |  |  |

| ASSP<br>-based Development                                                | Advance development of software:                  |  |  |  |  |

| HVV Specification   Logic design and verification   ES manufacturing      | Eight months ahead of schedule                    |  |  |  |  |

| SW Specification Advance evaluation/development                           | Software development                              |  |  |  |  |

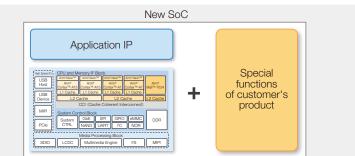

## **Example of ASSP-based Development**

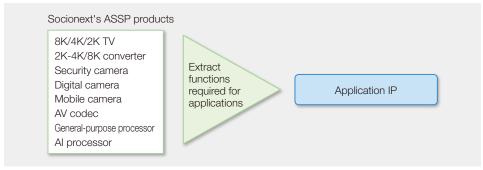

This section introduces one example of ASSP-based development.

① Extracting necessary application IP from ASSP

We extract application IPs which are required for customer's development from our proven ASSP.

2 Combining base platform and extracted application IP

After cutting down unnecessary IPs and Interfaces from base platform, then we combine this optimise platform and extracted application IP.

| Hgt Speed To<br>USB Amtheon <sup>111</sup> Amtheon <sup>112</sup> Amtheon <sup>114</sup> Amtheon <sup>1144</sup> Amtheon <sup>114</sup> Amtheon <sup>114</sup> Amtheon <sup>114</sup> Amtheon <sup>114</sup> | Application IP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USB L2 Cache L2 Cache L2 Cache<br>CCI (Cache Coherent Interconnect)<br>System Control Block<br>PCIe CTRL NAND UART PC NOR DDR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Use         CPU and Memory F Book           Use         Martissina durit lange         Same and<br>Same and<br>Sa |

| Media Processing Block SDIO LCDC Multimedia Engine IIS MIPI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Optim         Optim <th< td=""></th<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

③ Adding your special functions to differentiate from others

By adding your special functions to differentiate from others, your special SoC design is now created.

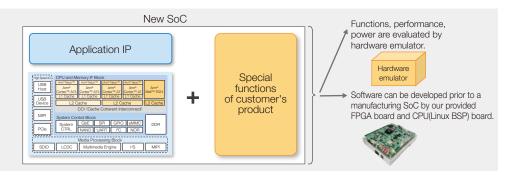

- 4 Evaluating and verifying functions, performance, and power

The functions, performance, and power can be evaluated and verified using a dedicated hardware emulator at approximately 1000 times as fast as an HDL simulator.

For your software development, we provide a prototype environment such as an FPGA board and CPU board. This allows customers to develop software before manufacturing SoC.

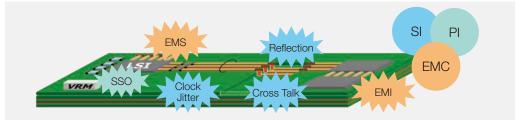

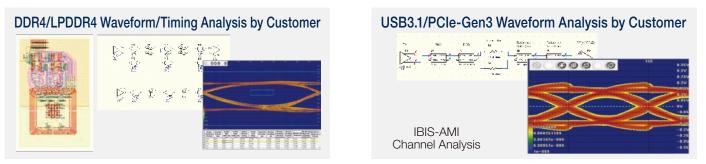

#### (5) PCB (printed circuit board) co-design

Implementing high-speed components (DDR, PCIe, USB, etc.) and SoC on a PCB tends to cause a electrical issue such as electromagnetic noise, crosstalk, and clock jitter. We analyze such issue creating PCB prototype and offer proposed measures.

This reduces risk associated with developing a PCB and thereby reduces cost for PCB design and manufacturing.

## **Full Custom Development**

To achieve the best performance of your SoC, we have full custom development option that allows you to customize as you like. For your full custom SoC development, we fully support for 1. proposing system architecture, 2. providing subsystem and a various of IPs, 3. optimized CPU peripheral design, and 4. system verification by hardware emulator and FPGA prototype. We also provide a device driver development service under contract as part of our software development support.

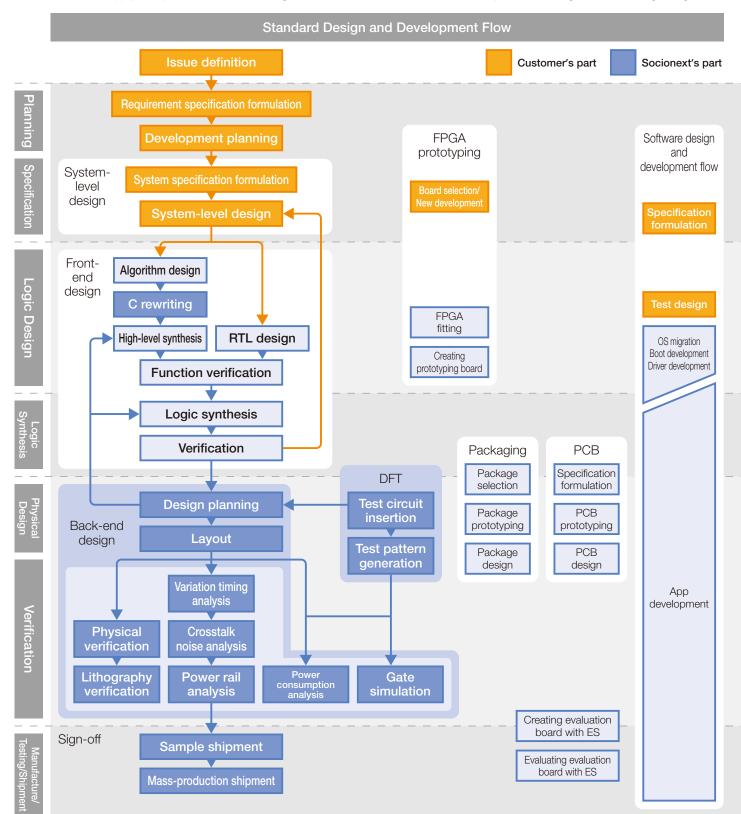

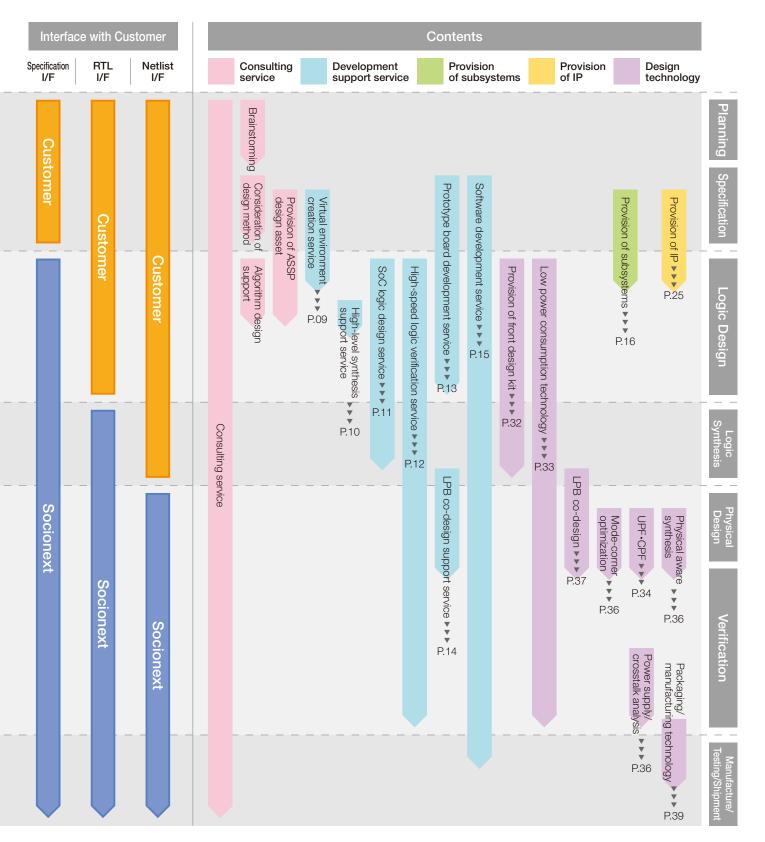

## Custom SoC Solution Map

At Socionext, we apply an optimized flow according to the features of the SoC to be developed, according to the following design flow.

# **Custom SoC**

## **User Interface**

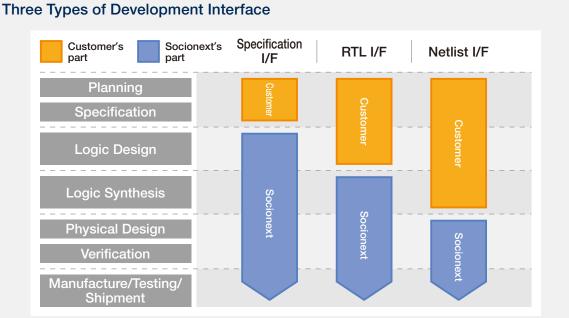

Socionext provides the three types of basic design interface shown below. The optimal combination of customers' design assets and our design technologies improves the efficiency of SoC development projects. We also provide a design flow that incorporates upstream verification and FPGA prototyping, supporting ever higher-quality projects and shorter development periods.

Specification interface

The specification interface method is used to interface with the customer based on the SoC design specifications. The customer will prepare a design specification document for the SoC to be developed. We will create an SoC development specification document based on those specifications, verify the logic design, and take care of everything right through to delivery of the SoC.

Interface RTL

The interface RTL method is used to interface with the customer based on design data (RTL) created by the customer through functional design. The customer will perform functional design through to verifying RTL. We will examine the test specifications, build a test circuit, and manage all processes through to SoC delivery.

Netlist interface

The netlist interface method is used to interface with the customer based on a netlist composed of our cells. The customer will perform tasks up to logic synthesis for netlist creation.

# Development Support Service (DesignExpress™)

## Development Support Service (DesignExpress™)

This design service provides you with consistent development support for everything from system specification to evaluation, as well as for PCB design, in every facet of custom SoC development. This service enables you to focus on your product development while shortening the development period, reducing risks associated with reworking, improving product quality, and reducing power consumption.

#### **Development Stages and Design Services**

| Devel | lopment stage | Use case fix/<br>software development<br>in advance | Performance<br>analysis | SoC logic verification/<br>software development<br>(~4MHz) | Software<br>development<br>(~50MHz) |

|-------|---------------|-----------------------------------------------------|-------------------------|------------------------------------------------------------|-------------------------------------|

| Des   | sign service  | Set up virtual<br>environment                       | SoC logic design        | High-speed logic verification                              | Prototype<br>development            |

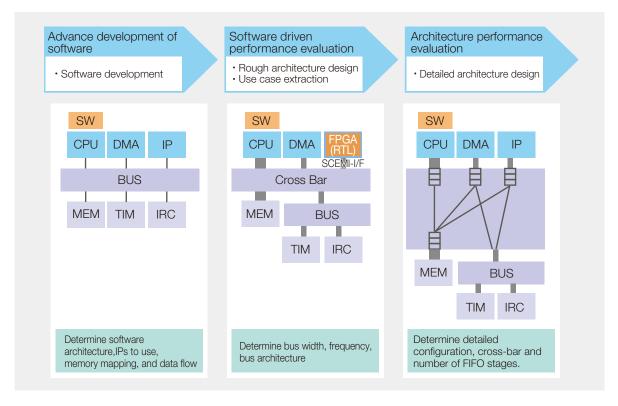

## Virtual environment creation service (Cedar<sup>™</sup>-ESL)

When considering SoC specifications and architecture, you only need to choose the services you actually need. Select from the following four menu items from the virtual environment creation service.

- · Virtual environment creation service for feasibility studies

- · Environment for measuring detailed bus architecture performance + Performance evaluation

- · Environment for advance development of software

- Environment for software-driven performance evaluation

| Service Category                                                              | Service Description                                                                                      | Item Submitted by Customer                                              | Deliverable from Socionext (Example)                                |

|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------------------------------------|

| Provide of development<br>environment for advance<br>development of software  | A virtual platform for<br>software development is<br>provided                                            | Block diagram<br>Block functional<br>specification                      | High-speed virtual platform (for software development)              |

| Provide of environment for<br>software driven performance<br>evaluation       | A virtual platform<br>for software driven<br>performance evaluation is<br>provided                       | Block diagram<br>Block functional<br>specification<br>Software scenario | High-speed virtual platform<br>(for architecture design)            |

| Provide of environment<br>for detailed architecture<br>performance evaluation | A virtual platform for<br>architecture performance<br>evaluation is provided.<br>Performance is measured | Architecture construction<br>diagram<br>Evaluation scenario             | High-accuracy virtual platform<br>Performance measurement<br>report |

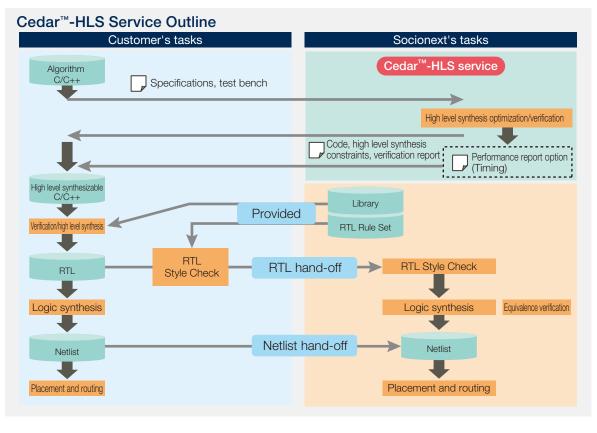

## High-level synthesis support service (Cedar<sup>™</sup>-HLS)

The high-level synthesis support service rewrites source code and provides a library that can be synthesized with that code. This tunes your source code into a high-level language (SystemC/C/C++) for adaption to the applicable process technology. After checking the consistency between the high-level synthesis results and the process technology to be used, we provide you with rewritten source code and the like.

| Service Category                                                         | Service Description | Item Submitted by Customer                   | Deliverable from Socionext (Example)                                                                           |

|--------------------------------------------------------------------------|---------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| Handing off of RTL<br>designed with high level<br>synthesis RTL hand-off |                     | Constraint conditions<br>High level language | Rewritten high level language<br>Library for high level synthesis<br>RTL designed with high level<br>synthesis |

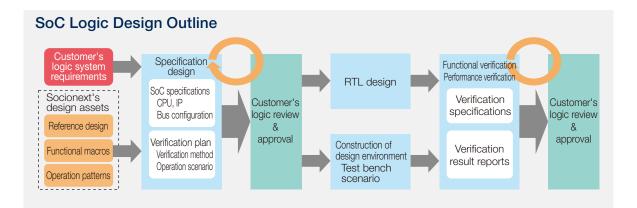

## SoC logic design service

With the SoC logic design service, Socionext will do the logic design on your behalf. In addition to complete SoC design, we can also do partial design. By combining various functional macros that we handle, we provide design data that best suits your system. Note that design data includes a functional specification document, RTL, and a verification report.

#### Service Category Service Description Item Submitted by Customer Deliverable from Socionext (Example) Specification design SoC specifications Requirement specifications Macros to be installed RTL design RTL SoC Logic Design Use cases Functional and performance Verification specifications, result **RTL** verification requirements reports

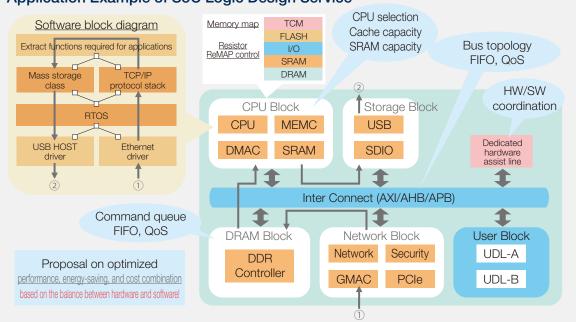

#### Application Example of SoC Logic Design Service

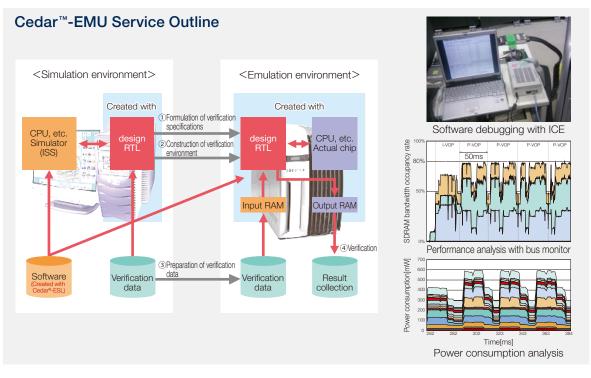

## High-speed logic verification service (Cedar<sup>™</sup>-EMU)

The high-speed logic verification service uses emulators and the like to perform high-speed logic verification and compute SoC power consumption. We can prototype a circuit by mapping a circuit of the system to be developed to an emulator. It can also compute your proposed system's power consumption. Since the emulator runs 500 to 1,000 times faster than a software simulator, you can significantly reduce verification time.

| Service Category            | Service Description                                                                                                                     | Item Submitted by Customer                                                         | Deliverable from Socionext (Example)                                               |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| Chip level verification     | Formulation of verification specifications<br>Creation of verification data<br>Construction of verification environment<br>verification | Outline block diagram<br>Design data (RTL or netlist)<br>Input/expected value data | Verification specifications<br>Verification data<br>Emulation verification results |

| System level verification   | System level verification using software developed in an ESL environment                                                                | Design data (RTL or netlist)<br>Input/expected value data<br>Test programs         | Emulation verification<br>environment<br>Verification result reports               |

| Power consumption reduction | Measurement of power consumption                                                                                                        | Power measurement program                                                          | Reports on results of power consumption measurement                                |

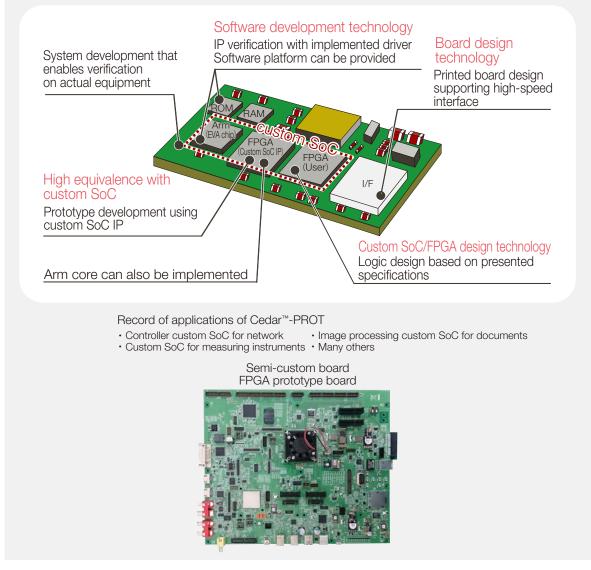

## Prototype Board Development Service (Cedar<sup>™</sup>-PROT)

The prototype board development service provides a prototype board for system-level verification and advance development of software. By implementing an IP equivalent to the IP to be installed on the system on an FPGA, this service provides a board that is equivalent to the target system. Since we can perform system-level verification and advanced software development before the SoC is completed, you can improve its quality and shorten the development period.

| Service Category Service Description |                              | Item Submitted by Customer            | Deliverable from Socionext (Example)                |

|--------------------------------------|------------------------------|---------------------------------------|-----------------------------------------------------|

| System level verification            | Provide of a prototype board | (specified circuit information, etc.) | Board unit<br>Board specifications<br>FPGA ROM data |

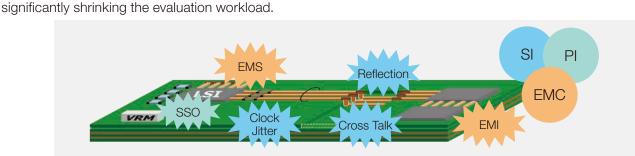

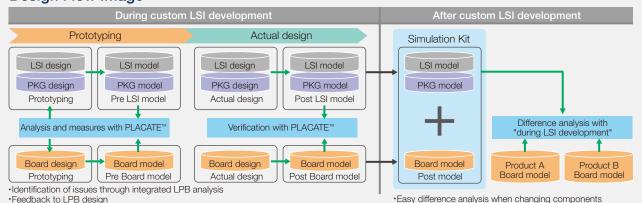

## LPB Co-design Support Service (PLACATE™)

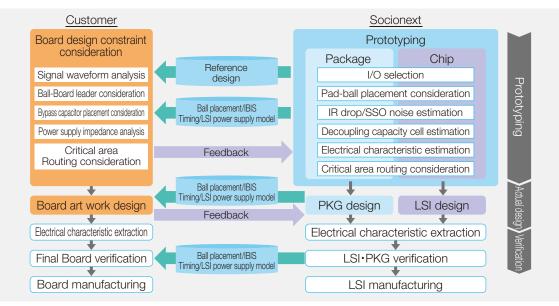

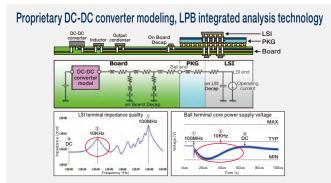

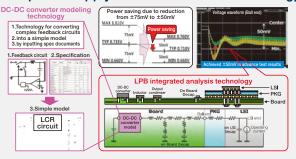

The LPB co-design support service analyzes noise and supports countermeasures based on an integrated LSI and Board model that help you to significantly shorten the system development period and reduce costs through reduced BOM. By applying this service from the upstream phase of LSI design and Board design, we help to cut your design time by reducing the amount of LSI and Board design rework that needs to be done, thereby improving their systems and

## Design Flow Image

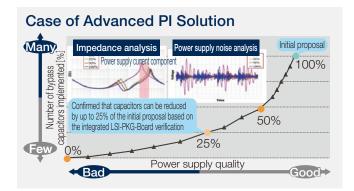

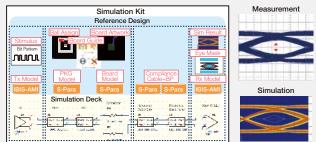

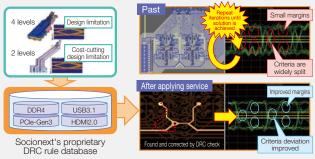

PLACATE<sup>™</sup> Service Description Deliverable (Example) 1.LPB design solution .Reference design 2.Core PI solution 2.DC-DC converter, report of 3.Advanced PI solution LPB integrated analysis results 4.EMC design solution 3.Reduce no. of parts by 5.DDRx solution centralizing power sources 6.SerDes solution 4.Report of EMC analysis results 7.LVCMOS solution 5.DDRx analysis report/simulation kit 8.Board DRC solution 6.SerDes analysis report/simulation kit .LVCMOS analysis report/IBIS model 8. Socionext's proprietary DRC rule database

## Structure of Simulation Kit

## Case of Board DRC Solution

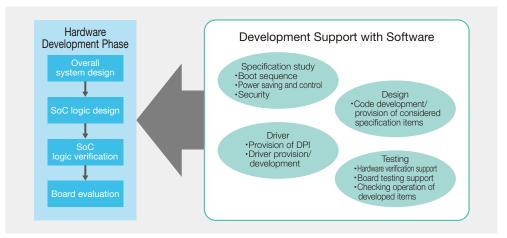

## Software Development Service

When reviewing the hardware specifications, it is important to examine the factors that form the basis of your SoC, such as the system startup sequence and power-saving features. After deciding on the specifications, these need to be embodied in software and checked in terms of the logic verification and board verification phases. We offer development support during such phases from the boot sequence to middleware development. In addition, through our services that cover the implementation of various OSs and the provision and development of device drivers, we support your system development efforts.

#### [Software Development Service]

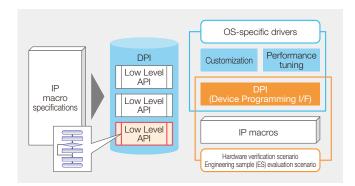

#### DPI (Device Programming Interface)

We provide basic functions such as the initialization, operation startup, and suspension of IP macros through program code.

- To check IP operation at an early stage (to be reflected in hardware verification scenarios)

- To develop device drivers in a short time (assisting the user in understanding specification documents, use of API)

- To quickly evaluate engineering samples (IP communication check, analysis)

#### Middleware for Subsystems

We provide middleware for subsystems and offer customization services that meet your specification requirements. For details, see the section on subsystems.

#### Linux/RTOS Support

We offer implementation of various OSs in addition to providing and developing device drivers.

#### **Examples of Development Support Services**

| Category      | Service Details                                                                                                                                                                                                                                                                                                                         |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Boot          | <ul> <li>Support for considering boot-sequence<br/>specifications</li> <li>Boot code design</li> <li>MAIN system startup-code design</li> <li>Secure boot-development support         <ul> <li>Proposal on secure boot sequence</li> <li>Secure boot implementation</li> <li>Secure boot-operation check support</li> </ul> </li> </ul> |  |

| IP driver     | Providing DPI for Socionext IP                                                                                                                                                                                                                                                                                                          |  |

| Linux support | OS migration support     Operation check support for provided drivers                                                                                                                                                                                                                                                                   |  |

| RTOS support  | OS migration support     Operation check support for provided drivers                                                                                                                                                                                                                                                                   |  |

| Power saving  | <ul> <li>Power-saving code design</li> <li>Providing and embedding network standby response code</li> </ul>                                                                                                                                                                                                                             |  |

# Subsystem Service

## Provide of Subsystems

Socionext provides subsystems featuring specific functions enabled by combining various types of IP. By incorporating a subsystem, the main system can achieve high performance with a specific function and low power consumption.

## Image Signal Processor Subsystem

#### Background and Initiatives

Under the current circumstances in which camera solutions continue to advance, it is extremely difficult to keep offering differentiating features. To address this issue, in 2017, we created IP for the image macro part of Milbeaut<sup>®</sup>, and began providing it as a high-resolution, high-performance subsystem. Furthermore, to meet future needs, we offer a line-up of IPs that are optimized for an extensive variety of applications in addition to high-grade cameras, which has been our main target in the past.

## Outline

By creating IP for an image macro for each functional block, it is possible to build a flexible platform. Each IP has the AXI interface so SoC integration is easy.

## Features

- High-performance 4Kp60 600Mpix/sec (ex TSMC 28nm HPC+)

- $\boldsymbol{\cdot}$  API for effectively using image macros is provided.

- An image adjustment simulator is provided to emphasize the individuality of images.

## Low light intensity noise reduction Defective pixel correction

#### Lens distortion correction

#### Lineup

| Lineup   |                              |                                                                                                                                                                                                  |  |  |

|----------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| IP Block | Function                     |                                                                                                                                                                                                  |  |  |

| B2B      | Bayer domain processing      | Noise reduction, resizing,<br>defective pixel correction, 3A<br>(AE/AWB/AF) statistics, shading<br>correction                                                                                    |  |  |

| B2R      | Demosaic<br>processing       | White balance gain, color interpolation                                                                                                                                                          |  |  |

| LTM      | Local tone mapping           | Local tone mapping                                                                                                                                                                               |  |  |

| R2Y      | RGB to YUV conversion        | Color correction, tone correction,<br>gamma correction, multi axis<br>color correction, YUV conversion<br>(444/422/420), edge enhancement<br>luminance noise reduction,<br>resizing, Y histogram |  |  |

| CNR      | Color noise reduction        | Color noise reduction,<br>purple fringing correction                                                                                                                                             |  |  |

| 3DNR     | Multi-frame noise reduction  | Noise reduction with reference to multiple images                                                                                                                                                |  |  |

| HDR      | High dynamic range synthesis | Dynamic range expansion by<br>synthesizing two different exposure<br>images                                                                                                                      |  |  |

| LDC      | Lens distortion correction   | Correction of image distortion<br>caused by optical characteristics                                                                                                                              |  |  |

## Arm<sup>®</sup> Processor Core Subsystem

## Arm Cores and Design Kits

The comprehensive license agreement with Arm allows customers to select the most suitable Arm core to meet their requirements. We provide the most suitable Arm core and SNAP-DK (design kit), a design environment, for custom SoC for a wide range of applications such as microcontrollers, embedded device, and application equipment.

These Arm Cores in the line-up are available on all process technologies that Socionext offers.

## Socionext Arm Platform (SNAP)

Use of the SNAP (Socionext Arm based SoC Platform) reduces development time and risks in Arm core-based SoC development. SNAP consist of the following.

#### Design Kits: SNAP-DK, ADK, SDK

- SNAP-DK : Consists of an Arm core and minimum required peripheral IPs.

- SNAP-ADK : SNAP-DK-based design kit that al-ready implements an interface macro, GPU, etc.

- SNAP-SDK : This design kit provides a fully customized dedicated subsystem for customers using a design tool in accordance with the requirement specifications.

By selecting the most suitable design kit based on the specifications customers require, development time can be reduced significantly.

These design kits, containing a simulation environment, test bench, sample boot code, etc., contribute to the shortening of time to launch the design environment and creation of an appropriate Arm core boot program.

#### Prototyping: SNAP-PK

- The SNAP-PK provides Socionext's unique FPGA board with SNAP-DK. By implementing a user logic on the FPGA side, it achieves prototyping of an SoC.

- This product can be used for system operation verification of hardware, performance evaluation, and early development of software.

#### Line-up of Arm Core, GPU and SNAP-DK

| Arm core |                |             |            |           |

|----------|----------------|-------------|------------|-----------|

| Arm v7   | Arm v8         | Arm v8      |            | available |

| Cortex-A | Cortex-A72     | Cortex-R52  | Cortex-A35 | planning  |

| Cortex-R | Cortex-A53     | Cortex-M33  | Cortex-A34 |           |

| Cortex-M |                | Cortex-M23  | Cortex-A32 |           |

| GPU      |                |             |            |           |

| Utgard   | Midgard        | Bifrost     |            |           |

|          |                | <b>G</b> 52 |            |           |

|          |                | <b>G</b> 31 |            |           |

| SNAP-DK  |                |             |            |           |

| OK-Av7   | <b>DK-A</b> 53 | DK-Av8      |            |           |

| OK-Rv7   |                | DK-Rv8      |            |           |

| OK-Mv7   |                | DK-Mv8      |            |           |

#### **SNAP Design Kits**

**SNAP-PK**

| Туре                                 |  | Content                                                                                   | Advantage                                                                                             |

|--------------------------------------|--|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| SNAP-DK<br>(Basic Design Kit)        |  | CPU<br>+ small-scale<br>peripheral IPs                                                    | Bootable CPU<br>subsystems can be<br>used                                                             |

| SNAP-ADK<br>(Advanced Design<br>Kit) |  | SNAP-DK<br>+ high performance IPs<br>(system with guaran-<br>teed performance)            | High performance<br>CPU subsystems<br>including an OS<br>can be used                                  |

| SNAP-SDK<br>(System Design Kit)      |  | Consultation-based<br>full custom design kit<br>(system with guaran-<br>teed performance) | Dedicated subsystems<br>based on requirement<br>specifications and<br>existing systems can<br>be used |

# <image>

## Video Codec Subsystem

## Background and Initiatives

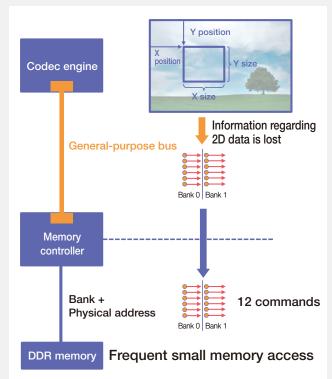

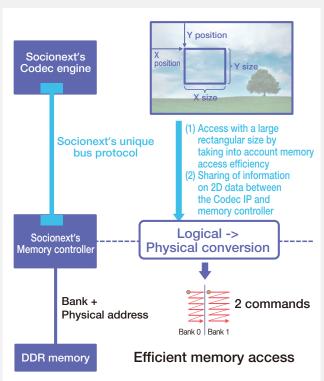

Due to an imbalance between the advance of DDR memory to the ultra-high speed generation along with an increase in the burst length and access by video codec processes handling small size rectangular image data to the DDR, a reduction in the efficiency of using the DDR memory band width has become an issue. This subsystem enables high efficiency video codec processing that can save the band width using Socionext's unique technology.

#### Outline

We have developed our unique bus protocol methodology that can improve memory access efficiency in the codec process without being significantly affected by advances in DDR.

Tightly coupling our codec engine and our memory controller with the methodology enables the memory

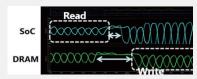

## General Relationship between Codec IP Core and DDR Memory

controller to efficiently access DRAM by taking into account a physical memory map based on the 2D information on image data accessed by the codec engine, reducing the required memory band width significantly.

#### Features

• Achieves various types of HEVC codec processing with a smaller bus width (bit) as listed below.

#### Example: When using LPDDR4 2400 Mbps

|        | Processing details | Socionext's<br>conventional<br>system | Video codec<br>subsystem |

|--------|--------------------|---------------------------------------|--------------------------|

|        | 4k 60p 4:2:2 10bit | 112bit                                | 64bit                    |

| Decode | 4k 60p 4:2:0 10bit | 96bit                                 | 48bit                    |

|        | 4k 60p 4:2:0 8bit  | 64bit                                 | 32bit                    |

|        | 4k 60p 4:2:2 10bit | 96bit                                 | 48bit                    |

| Encode | 4k 60p 4:2:0 10bit | 80bit                                 | 48bit                    |

|        | 4k 60p 4:2:0 8bit  | 64bit                                 | 32bit                    |

#### Relationship between Socionext Codec IP Core and DDR Memory

## IP Video Streaming Subsystems

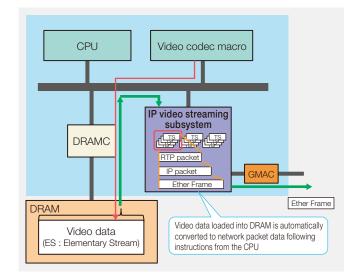

#### Background and Initiatives

With the spread of the Internet, demand for video streaming is exploding. Typical examples are media servers for downstreaming and network monitoring cameras for upstreaming. In such target areas, Socionext carries out fragmentation and IP packetization of video data after codec processing, significantly reducing the processing load of the main system.

#### Outline

This subsystem encapsulates video and audio data into an IP packet and encapsulates the IP packet into an Ethernet frame. The high-performance IP macro executes the following series of processes just by placing data after codec processing.

- Packetizing video data (ES: elementary stream, loaded into DRAM) into TS packets

- Encapsulating ES, TS, or JPEG data into RTP packets

- Encapsulating RTP packets into IP packets

- Encapsulating IP packets into Ethernet frames and performing GMAC control (video transmission)

#### Features

- Support for RTP/UDP offloading [Supported formats]

- ES over RTP: Video (H.264), Audio (G.771, AAC)

- JPEG over RTP

- TS over RTP

- Metadata over RTP

- Support for Max. 32 streams

- · Integration with security (encryption) functionality

| Transfer band (Mbps)                            | 10 | 30 | 50  | 150 | 300 | 500 |

|-------------------------------------------------|----|----|-----|-----|-----|-----|

| Offloading not available<br>CPU load factor (%) | 23 | 62 | 100 |     |     |     |

| Offloading available<br>CPU load factor (%)     | -  | -  | 15  | 21  | 29  | 39  |

Load reduced by 25 times

## HDMI 2.1-Compatible Data Transmission and Reception Subsystem

#### Background and Initiatives

The HDMI 2.1 specifications were defined in 2017. It has 48-Gbps bandwidth, 2.7x that of conventional HDMI 2.0, and enables the transmission of extremely large data sets, including 8K video, with very low latency while maintaining high image and sound quality. With our extensive knowledge in developing of data-transmission technologies for consumer video equipment such as recorders and 4K TVs, as well as for high-speed, serial data transmission used in large-scale servers, Socionext offers HDMI 2.1 compatible data transmission and reception subsystem (Link/PHY).

#### Outline

This subsystem supports the HDMI 2.1 (High-Definition Multimedia Interface) specification. It supports video resolution of up to 4320 x 7680p and color depth of 8, 10, and 12 bits, and covers a bandwidth of 48 Gbps (4Lane). While supporting L-PCM audio data and compressed audio data, the subsystem supports high bit-rate audio (up to 768 kHz) as well as sampling rates from 32 kHz to 192 kHz.

#### Features

- Support for VESA DSC 1.2a

- Support for Dynamic HDR and eARC

- Support for game mode VRR/QMS

- Support for HDCP2.3

- Support for hot plug detection

#### HDMI 2.1-Tx output waveform @ 12 Gbps

#### Compliance test (protocol) evaluation environment

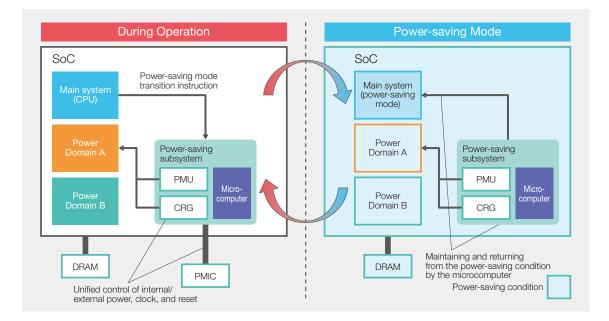

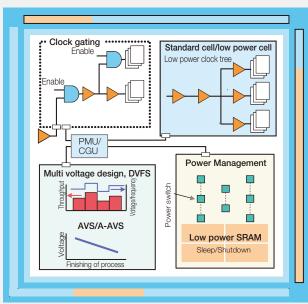

## Power-saving Subsystem

#### Background and Initiatives

In step with SoCs becoming more functional and highly integrated recently, providing a power-saving mode has become an absolute essential. For example, network standby mode keeps the minimum required interfaces, mainly network functions, awake and places the remaining functions in standby to save power. Sleep mode keeps only subsystems awake to make the system enter a deeper sleep, and there are various ways to implement power-saving mode. We provide a power-saving system to satisfy such needs.

#### Outline

A power-saving subsystem is composed of an Arm microcomputer, minimum required peripheral IP, RAM, and others, and operates separately from the main system. By doing so, this subsystem allows you to achieve the following functions.

- Transition and return from power-saving mode with a simple instruction from the main system to the subsystem

- · Achieve deep-sleep mode by keeping only the subsystem awake

- · Integrate the power-up and shut-down sequences

We offer the following support services that make it easy to introduce the subsystem.

- · Support for considering system power-saving sequences between the main system and subsystem

- · Software design support for main system sleep and wake-up scenarios

- · Design support for controlling the subsystem power supply

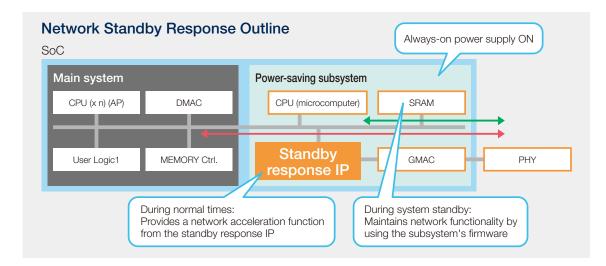

## Network Standby Response

Network standby response is a function in which the subsystem carries out packet processing on behalf of the main system when it is in a standby state. This function also supports the following functions.

[Supported functions]

- Main system wake-up assistance when a packet requiring processing by the main system is received

- The acceleration function that accelerates packet processing in a normal state

#### Actual Network Standby Response Performance Values

| Function/Performance      | Normal           | When using proprietary technology    | Comparison      |

|---------------------------|------------------|--------------------------------------|-----------------|

| Stand-by power            | 2 W to several W | <100mW                               | <1/20           |

| Communication performance | 300Mbps          | 900 Mbps (20% reduction in CPU load) | Approx. 3 times |

Actual measurements with MB86S73 board

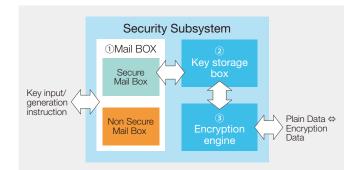

## Security Subsystem

#### Background and Initiatives

With the recent progress of the IoT (Internet of Things), a security system has become an essential item. Although a high level of protection for secret information and high-speed algorithm processing by hardware are indispensable for a security system, it is not easy to develop such hardware and software from scratch. Using Socionext's security subsystem can reduce the burden of such development, making it possible for you to introduce a security system efficiently.

#### Outline

The security subsystem includes a dedicated key storage box to store highly secret key information. It also incorporates a hardware engine that uses the stored key to perform high-speed encryption and authentication processing, achieving a high-level security system.

[Features of the security subsystem]

- Secure key generation and input through a dedicated e-mail box

- ②Secure key storage through locating key storage in a module

- ③A dedicated engine that uses a key in a secure key storage box

The following presents an example function using this subsystem and system configuration.

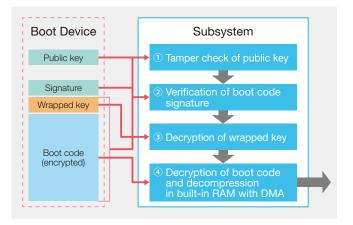

#### Example Function Using Subsystem: Secure Boot

The boot code is executed at the beginning of system startup, and whether a correct program is used or not must be examined on the basis of the boot code. It is the key for a security system where such important code is encrypted and stored, and a mechanism is in place to detect whether such code has been altered. The security subsystem provides a mechanism to protect and securely execute such important code.

# **Custom SoC**

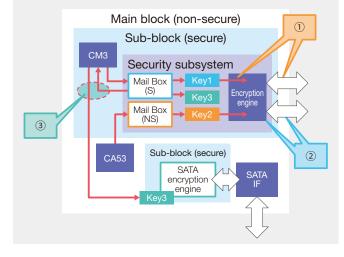

Example of System Configuration Using Subsystem

The security subsystem can be applied as follows for the entire system.

- Secure boot from a micro computer in a secure sub-block and ROM

- ② Creation of a dedicated key storage route and encryption processing for a non-secure main block

- ③Key management for another encryption engine by using the security subsystem and a microcomputer in a secure sub-block

#### Hardware Accelerator

The following shows a list of security algorithm accelerators installed in the subsystem.

| Syste                   | m        | Key Length (bit) |

|-------------------------|----------|------------------|

| Common key encryption   | 3DES-ECB | 168              |

|                         | 3DES-CBC | 168              |

|                         | AES-ECB  | 128/192/256      |

|                         | AES-CBC  | 128/192/256      |

|                         | AES-CTR  | 128/192/256      |

|                         | AES-GCM  | 128/192/256      |

| Hash                    | SHA-1    | -                |

|                         | SHA-256  | _                |

|                         | SHA-512  | _                |

| HMAC                    | SHA-1    | 160              |

|                         | SHA-256  | 256              |

|                         | SHA-512  | 512              |

| Electronic signature    | RSA      | 2048 - 3072      |

| generation/verification | ECDSA    | 256/384/521      |

# **IP Macro Service**

## Line-up of IP Macros

Socionext's IP macros with their proven track records support customers in advanced SoC development.

## Functional/Interface Macros

✓ : Available ✓ : In development

|                              |                   | Process Technology |           |      |      |           |         |

|------------------------------|-------------------|--------------------|-----------|------|------|-----------|---------|

| Category                     | Function          | 90nm               | 65nm/55nm | 40nm | 28nm | 16nm/12nm | 7nm/6nm |

|                              | Cortex-A          | 1                  | 1         | √    | 1    | 1         | 1       |

|                              | Cortex-R          | 1                  | 1         | 1    | 1    | 1         | 1       |

| Arm Cores                    | Cortex-M          | 1                  | 1         | 1    | 1    | 1         | 1       |

|                              | Arm11, Arm9, Arm7 | 1                  | ✓         | 4    | 1    | 1         | 1       |

|                              | Mali              | 1                  | ✓         | 1    | 1    | 1         | 1       |

|                              | JPEG              | 1                  | 1         | 1    | 1    | 1         | 1       |

| Image Core                   | H.264             | 1                  | 1         | 1    | 1    | 1         | 1       |

|                              | H.265             | 1                  | 1         | 1    | 1    | 1         | 1       |

|                              | SHA               | 1                  | 1         | 1    | 1    | 1         | 1       |

| Socurity Coro                | РКА               | 1                  | 1         | 1    | 1    | 1         | 1       |

| Security Core                | 3DES              | 1                  | *         | 4    | 1    | 1         | 1       |

|                              | AES               | 1                  | 1         | √    | 1    | 1         | 1       |

| Interface<br>Controller Core | OSPI/QSPI         | 1                  | 1         | 1    | 1    | 1         | ~       |

|                              | UART              | 1                  | 1         | 1    | 1    | 1         | 1       |

|                              | UHS-I             | 1                  | 1         | 1    | 1    | 1         | ~       |

| SD                           | UHS-II            |                    |           |      | 1    | 1         | ~       |

## High Speed Interface Macros

|                | Function                         | Process Technology |           |      |      |                       |              |

|----------------|----------------------------------|--------------------|-----------|------|------|-----------------------|--------------|

| Category       | Function                         | 90nm               | 65nm/55nm | 40nm | 28nm | 16nm/12nm             | 7nm/6nm      |

|                | USB3.1 Gen2 Host/Device          |                    |           |      | 1    | 1                     | ~            |

| USB            | USB3.1 Gen1 (USB3.0) Host/Device |                    | 1         | ✓    | 1    | 1                     | ~            |

|                | USB2.0 Host/Hub/Device           | 1                  | 1         | ✓    | 1    | <ul> <li>✓</li> </ul> | ~            |

| Ethernet       | Gigabit Ethernet MAC             | 1                  | 1         | ✓    | 1    | 1                     | 1            |

|                | HDMI2.0                          | 1                  | 1         | ✓    | 1    | 1                     | ~            |

| ) /ideo        | HDMI2.1                          |                    |           |      | 1    | 1                     | ~            |

| Video          | V-By-One HS                      |                    |           | ✓    | 1    |                       |              |

|                | FPD-Link                         | 1                  | 1         | ✓    | 1    |                       |              |

|                | LVDS                             | 1                  | 1         | ✓    | 1    | 1                     | ~            |

| LVDS           | SubLVDS                          | 1                  | 1         | ✓    | 1    | 1                     | ~            |

|                | DSI TX                           | 1                  | 1         | ✓    | 1    | 1                     | 1            |

|                | CSI-2 TX/RX                      | 1                  | 1         | ✓    | 1    | 1                     | 1            |

| MIPI           | D-PHY                            | 1                  | 1         | ✓    | 1    | 1                     | ~            |

|                | C/D-PHY                          |                    |           |      | 1    | 1                     | ~            |

|                | M-PHY                            |                    |           |      | 1    | 1                     | ~            |

|                | PCIe Gen4 RT/EP                  |                    |           |      |      | 1                     | ~            |

| PCI<br>Express | PCIe Gen3 RT/EP                  |                    |           |      | 1    | <ul> <li>✓</li> </ul> | $\checkmark$ |

|                | PCIe Gen2 RT/EP                  |                    | 1         | ✓    | 1    |                       | ~            |

(continued on the following page)

# **Custom SoC**

## High Speed Interface Macros

✓ : Available ✓ : In development

| Cotocorri         | Function     | Process Technology |           |      |      |              |              |

|-------------------|--------------|--------------------|-----------|------|------|--------------|--------------|

| Category          |              | 90nm               | 65nm/55nm | 40nm | 28nm | 16nm/12nm    | 7nm/6nm      |

|                   | SATA3 AHCI   |                    |           | ✓    | 1    | 1            |              |

| Serial ATA        | SATA2 AHCI   | 1                  | 1         | ✓    |      |              |              |

|                   | SATA3 Device |                    |           | ✓    | 1    | 1            |              |

|                   | DDR3         | 1                  | 1         | ✓    | 1    | 1            |              |

|                   | DDR3L        | 1                  | 1         | ✓    | 1    | 1            |              |

|                   | DDR4         |                    |           | ✓    | 1    | 1            |              |

| DRAM<br>Interface | LPDDR3       |                    |           | ✓    | 1    | 1            |              |

| (PHY)             | LPDDR4       |                    |           |      | 1    | 1            |              |

|                   | LPDDR4X      |                    |           |      |      | 1            |              |

|                   | LPDDR5       |                    |           |      |      | $\checkmark$ | $\checkmark$ |

|                   | HBM2         |                    |           |      |      | 1            |              |

## Analog Macros

| Catamarri             | Eurotion                                |      | Process Technology |      |                       |           |              |  |

|-----------------------|-----------------------------------------|------|--------------------|------|-----------------------|-----------|--------------|--|

| Category              | Function                                | 90nm | 65nm/55nm          | 40nm | 28nm                  | 16nm/12nm | 7nm/6nm      |  |

|                       | 10bit, up to 600MS/s                    | 1    | 1                  | 1    | 1                     | 1         |              |  |

| ADC                   | 12bit, up to 200MS/s                    | 1    | 1                  | 1    | 1                     | 1         | ~            |  |

|                       | 16bit                                   | 1    |                    |      | 1                     | 1         |              |  |

|                       | 10bit, up to 220MS/s                    | 1    | 1                  | ✓    | 1                     |           |              |  |

| DAC                   | 12bit, up to 110MS/s                    | 1    | ✓                  | ✓    |                       |           |              |  |

|                       | 16bit                                   | 1    | ✓                  |      |                       |           |              |  |

|                       | Audio                                   |      |                    | ✓    | 1                     |           |              |  |

| AFE                   | Video                                   |      |                    | ✓    | 1                     |           |              |  |

|                       | Scanner                                 |      |                    | 1    | <ul> <li>✓</li> </ul> |           |              |  |

| Temperature<br>sensor | +/-5deg.C accuracy (without trimming)   |      | *                  | 1    | ~                     | 1         | $\checkmark$ |  |

| Power                 | Vin=3.3V, Vout=1.0-1.2V, Iout≦400mA LDO | 1    | ✓                  | √    | 1                     | 1         |              |  |

| management            | Power on reset                          |      |                    | 1    | 1                     | 1         |              |  |

|                       | Fout: ~1200MHz, Fin:10~200MHz           | 1    | ✓                  | ✓    | 1                     | 1         |              |  |

|                       | Fout: ~1600MHz, Fin:16~200MHz           | 1    | ✓                  | ✓    | 1                     | 1         |              |  |

| Standard PLL          | Fout: ~2400MHz, Fin:16~200MHz           |      |                    | 1    | 1                     | ✓         | $\checkmark$ |  |

|                       | Fout: ~3200MHz, Fin:16~200MHz           |      |                    |      | ✓                     | ✓         | $\checkmark$ |  |

|                       | Fout: ~5000MHz, Fin:20~100MHz           |      |                    |      | 1                     | ✓         | $\checkmark$ |  |

|                       | Fout: ~600MHz, Fin:11~100MHz            | 1    | 1                  | 1    | 1                     | 1         |              |  |

| Low Jitter PLL        | Fout: ~1000MHz, Fin:10~40MHz            |      |                    | 1    | 1                     | 1         | $\checkmark$ |  |

|                       | Fout: ~6400MHz, Fin:20~100MHz           |      |                    |      | 1                     | 1         | $\checkmark$ |  |

| Fractional -N         | Fout: ~1600MHz, Fin:10~50MHz            | 1    | ✓                  | 1    | 1                     | 1         |              |  |

| PLL                   | Fout: ~3200MHz, Fin:10~50MHz            |      |                    |      | 1                     | 1         | $\checkmark$ |  |

|                       | Fout: ~1600MHz, Fin:10~50MHz            | 1    | 1                  | ✓    | 4                     | 1         |              |  |

| SSCG                  | Fout: ~2400MHz, Fin:20~50MHz            |      |                    | 4    | 1                     | ✓         | $\checkmark$ |  |

|                       | Fout: ~3200MHz, Fin:10~50MHz            |      |                    |      | 1                     | 1         | $\checkmark$ |  |

## Interface Macros

## **DDR Interface**

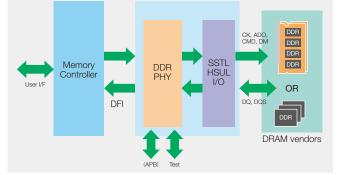

Socionext provides various DDR interface macros from low-to-middle speed forwarding bandwidth to high-speed forwarding bandwidth or low power, with various process technologies. Moreover, we support development for signal quality and cost optimization through design support by Chip-Package-Board co-design.

#### DDR interface macros

- · High-speed/high-bandwidth DDR3/DDR4

- · Low power

- LPDDR4X/4/3/2 DDR3L

- DFI compliant (all macro)

- Compatible with many different DRAM configurations and PKG options, such as Fly-by, PoP, and DIMM thanks to the PHY function (training function).

#### DDR interface design support (Chip-Package-Board codesign)

- Timing verification : Verifies the timing of all DDR-IF systems including delays between LSI I/O and DRAM

- Power Integrity : Optimizes the parasitic inductance, resonant frequency, and power supply (PKG, PCB) impedance as part of the power supply impedance design

- Signal Integrity : Optimizes Driver strength, terminator resistance, and interconnect topology

- Bus switching verification

: Optimizes the write and read bus switch timing

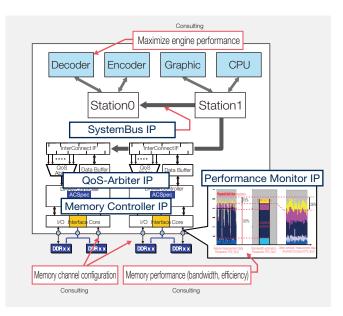

## **Memory Controllers**

Socionext provides various memory solutions for system optimization. We also offer consulting services on memory systems including memory channels and the system bus to maximize SoC performance.

- Memory controller IP

- Controller for maximizing high DRAM utilization

- QoS-Arbiter IP

- High performance QoS-Arbiter featuring multiple functions

- BusIP

- · Original low power consumption bus with high layout flexibility

#### MonitorIP

- Visualizes memory system performance in real-time

- Monitors performance (bandwidth, latency) and provides an environment for tuning parameters

**DDR Interface Configuration Diagram**

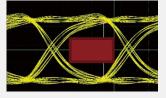

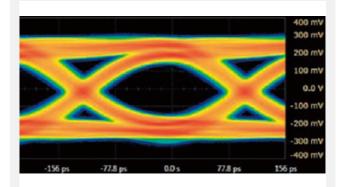

#### LPDDR4-3733 DQ Waveforms

#### **Bus Switching Waveforms**

# **Custom SoC**

## **MIPI Interface**

This high-speed interface is used to build a camera and display system by combining high-speed, high resolution CMOS image sensors. This interface provides a solution for highly expressive images.

#### MIPI D-PHY TX macro

Small footprint, high-performance macro with the maximum speed of 4.5 Gbps

- 4-data lane + 1-clock lane configuration

- Transmission speed: 80 Mbps to 4.5 Gbps per lane

- Equalization function

- The world's smallest footprint

- D-PHY2.0 compliant

## **PCI Express Interface**

As a result of the recent rapid improvement in CPU processing capability and an increase in the need for high capacity data transfer, it has become extremely difficult to achieve the expected system performance with existing buses. The PCI Express technology is a high-speed interface capable of transferring several hundred megabytes of data that can overcome this issue.

Socionext's PCI Express macro supports up to 8 GT/s (Gen3) and passed the PCI Express standard compliance test hosted by the Peripheral Component Interconnect Special Interest Group (PCI-SIG), and its interconnectivity and reliability have been confirmed with many PCI Express interfaces.

#### PCI Express LINK macro

- Compliant with the PCI Express Base Specification

rev.3.0 standard specification

- Support for x1, x4, and x8 lanes

- DualMode (RootComplex or Endpoint is selectable)

- · Possible to select AMBA3 I/F as the user interface

- Built-in DMAC

#### PCI Express PHY macro

- Maximum transfer bit rate of 64 GT/s

- High-speed signal transmission with the deemphasis function is guaranteed

- The LINK macro interface is compliant with the PIPE3 and PIPE4 standard specifications

#### D-PHY TX Output Waveforms at 4.5 Gbps

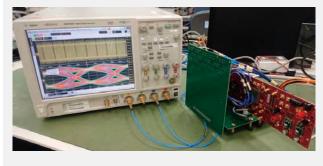

#### PCI Express Gen3 Evaluation Environment

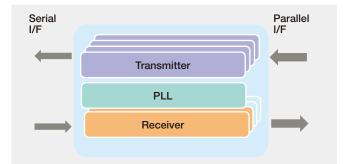

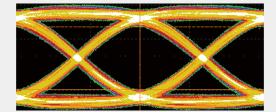

## 10G-28Gbps SerDes Interface

With transmission performance of 10Gbps–28Gbps per channel and a configuration comprised of multiple channels, we provide a high-performance SerDes macro for constructing 100G/200G/400G optical networks or 100G Ether systems.

The built-in low-jitter, high-performance PLL enables robust transmission up to 28 Gbps per channel.

It also supports various standards including OIF-CEI-11G-SR, OIF-CEI-28G-SR, OIF-CEI-28G-VSR, IEEE802.3ba CAUI, IEEE802.3bm CAUI4, XFI and so forth.

- $\times$ 1,  $\times$ 4 lane configuration.

- Comprised of Transmitter/Receiver/PLL and capable of bidirectional communication with 1 macro.

- Up to 112.8 Gbps per macro (for unidirectional, ×4 configuration).

- Support for power-down control on each lane.

- Support for power-down control for the entire macro.

- Implementing Clock-Data Recovery for each Receiver lane.

- Transmitter Equalization supported.

- Receiver Equalization supported.

- · Built-in termination resistor in Transmitter/Receiver.

- Organic flip chip package.

- (0.8 mm/1.0 mm Ball Pitch, HDBU Package)

28 Gbps Output Waveforms with Test Chip

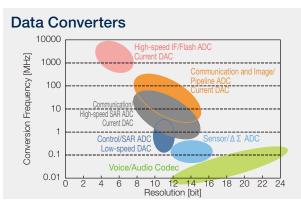

## Analog Macros

We offer various analog macros (data converter, power management, temperature sensor, analog front-end) for our customers' development to address various applications including communication, image processing, sensors and control.

- · All macros are silicon verified.

- Implemented on many custom SoCs with a track record in mass production.

## Data Converters

We offer various data converter macros addressing low power consumption and a small area which are demanded in SoCs.

#### Pipeline & high speed SAR ADC

- ·10-bit/12-bit resolution, maximum 600MSPS conversion rates

- The world's smallest class power consumption

#### ΔΣ ADC

- Applicable to 16bit to 24bit resolutions

- · Power consumption of up to 1 mW with high precision SINAD 85 dB

- ΟΔΣ DAC

- Applicable to 16bit to 24bit resolutions

- SINAD 90 dB. Power consumption is 1 mW or less

## Power Management

We offer various power management macros that enable single power supply development which is demanded in SoCs.

#### LDO for low-noise power supply applications

- · Lineup of small-area versions such as the integrated I/O type

- · Safety protection functions such as short-circuit detection

- · Supports power supply to analog IPs such as ADC and PLL

- Power-ON reset

- · Customizable voltage-detection level and reset time

- Supports brown-out reset

#### External 3.3-V power LDO supply

(1.2V)

**Example Application of Power Management Macro**

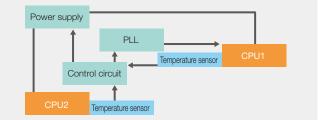

## Sensors and Analog Front-End (AFE)

We offer a sensor macro for measuring temperature and voltage inside the chip and a low power-consumption AFE for processing signals from various external sensors.

#### Temperature sensor macro

- Can monitor temperature inside the chip at high resolution (0.125° C)

- Low power consumption and small area allow installation of multiple sensors on one chip

- Realizes temperature-dependent voltage and frequency control system

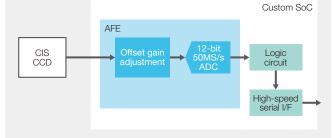

#### Scanner AFE

- Supports both CCD and CIS

- Includes gain and offset adjustment function

- Comes with 12-bit, 50 MS/s ADC

- Low power consumption (19 mW)

- Custom AFE that supports various sensor signals and external signals

- AFE for optical sensor, humidity sensor, and gyro sensor

- Video AFE

- Audio AFE

- Digital TV AFE

#### Example Application of Temperature Sensor

#### **Example Application of Scanner AFE**

# Design Technology

## Front-end Design

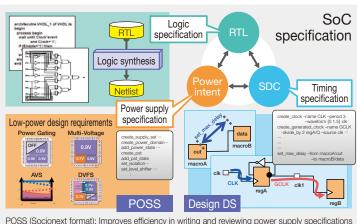

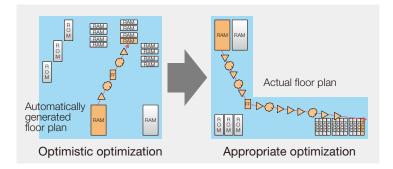

## Front-end Design kit

We offer a development environment using standard EDA tools as a SoC development environment for customers and a tool we created for improving design efficiency as a design kit. The front-end design kit, which is uniquely optimized by Socionext, enables the development of high performance, small chip size, low power LSIs.

| ED/ (tools supported by booldhext from the design fit |             |                                                                                                               |  |  |

|-------------------------------------------------------|-------------|---------------------------------------------------------------------------------------------------------------|--|--|

| High level synthesis                                  |             | Catapult <sup>*3</sup> , C-to-Silicon Compiler <sup>*1</sup> , Stratus <sup>*1</sup>                          |  |  |

| RTL style check Sp                                    |             | SpyGlass*2                                                                                                    |  |  |

|                                                       | Verilog-HDL | Incisive Enterprise Simulator *1, Questa *3, VCS-MX,VCS *2                                                    |  |  |

| Functional verification                               | VHDL        | Incisive Enterprise Simulator *1, Questa *3, VCS-MX *2                                                        |  |  |

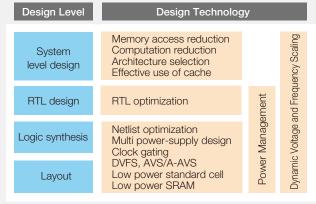

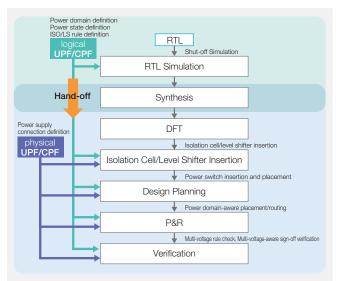

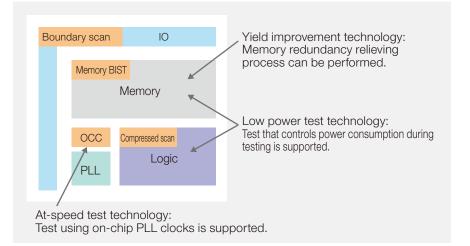

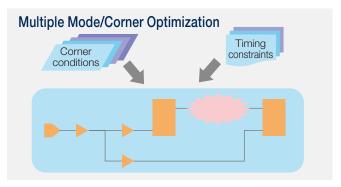

|                                                       | CPF/UPF     | Incisive Enterprise Simulator-XL <sup>*1</sup> , Questa <sup>*3</sup> , VCS-NLP <sup>*2</sup>                 |  |  |