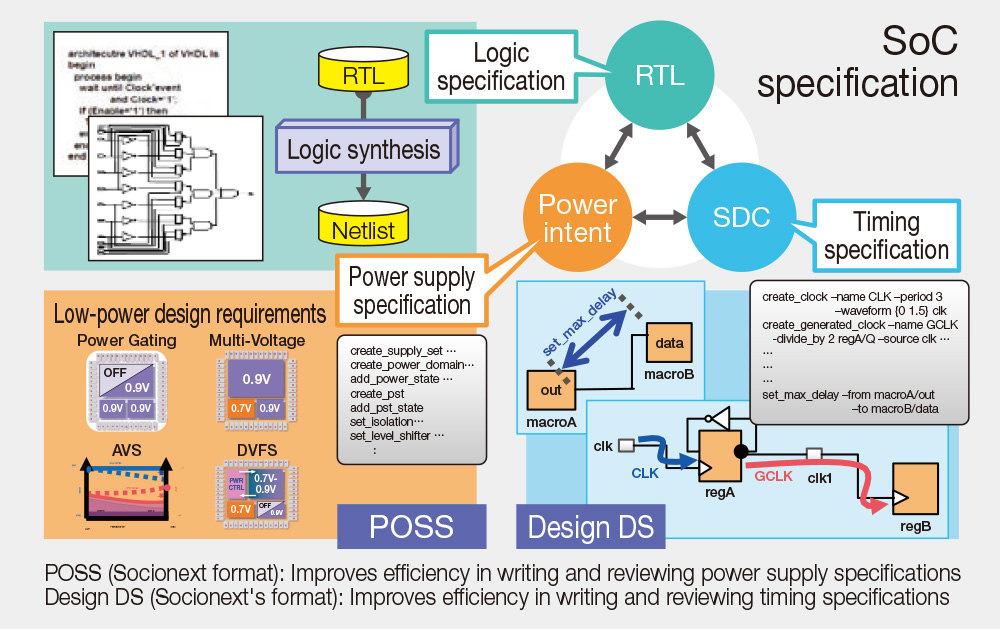

Design Specification Interface

Designing a System-on-Chip (SoC) involves more than just RTL (Register Transfer Level) and netlist data for logic design. It also requires power intent information, such as the SDC (Synopsys Design Constraints) file that describes timing specifications (including clock frequency), and CPF/UPF (Common Power Format/Unified Power Format) files containing power supply specifications (including power gating design and multi-power/multi-voltage design). Our unique interface files provide a convenient format for managing this power intent. By using these files, you can enhance efficiency in writing and reviewing specifications, ensuring consistency between the RTL, power supply specs, timing requirements, and layout compatibility.

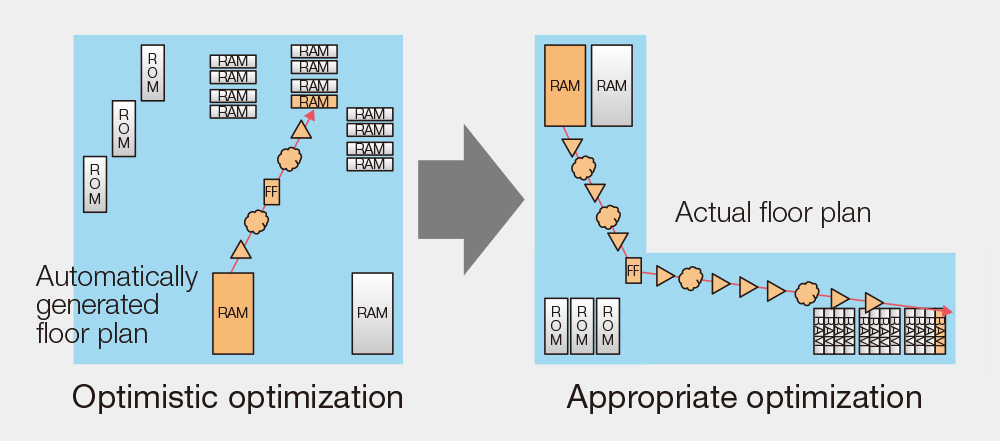

Physical aware Logic synthesis

Due to advancements in technology, considering layout during logic design has become crucial for enhancing System-on-Chip (SoC) design efficiency and optimizing area and timing. To achieve this, we employ physical-aware synthesis, which optimizes based on the actual layout. By integrating logic design and layout design, we can efficiently create sophisticated SoCs tailored to your product.