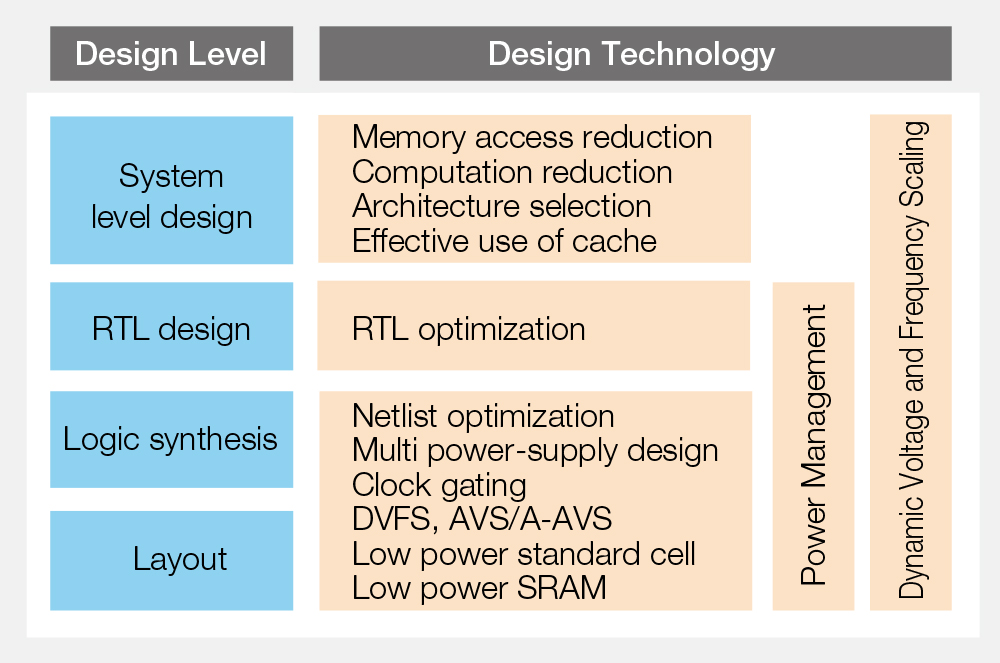

The demand for reducing the power consumption of LSIs has grown significantly in recent years. In our SoC design efforts, we are implementing various initiatives to address customers’ requests for lower power consumption.

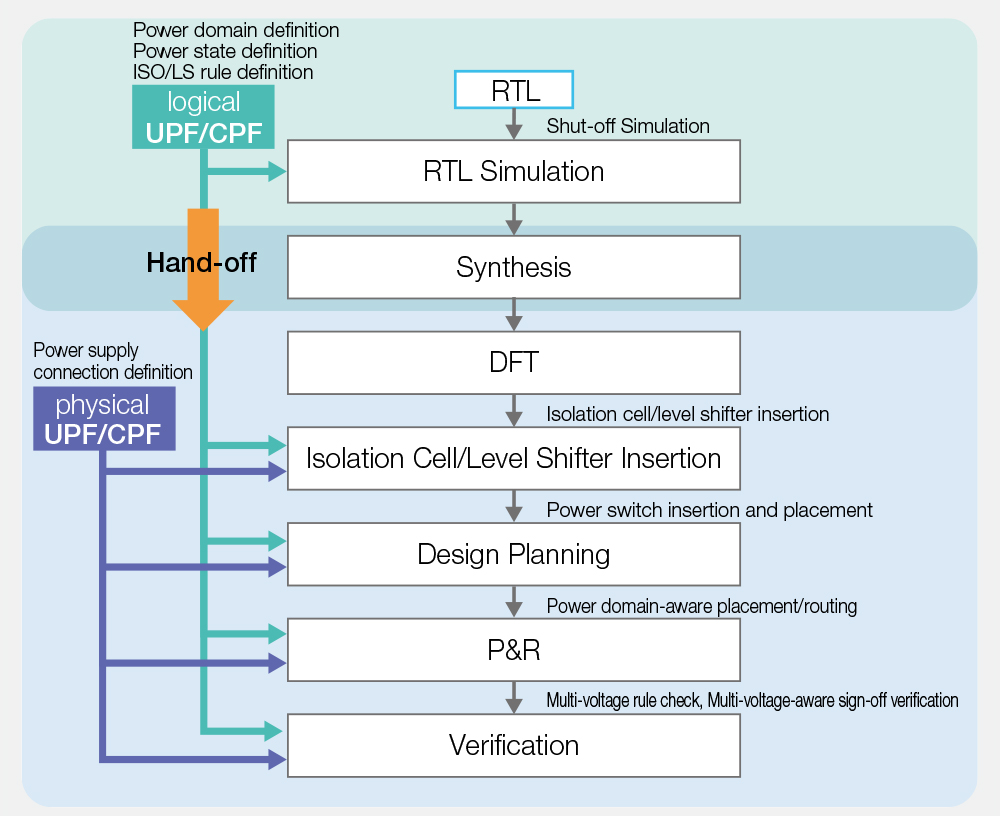

To achieve low power consumption LSIs, combining different technologies and leveraging individual approaches is effective. Socionext’s design environment, known as the ‘Reference Design Flow,’ supports a range of low power consumption technologies. This environment allows us to reduce LSI power consumption during both active operation and standby modes. By specifically controlling the power supply, we develop systematic methodologies for achieving low power consumption. Additionally, by fully adopting UPF/CPF (Unified Power Format/Common Power Format), we simplify low-power design for our customers while minimizing changes to their existing design assets

Multi-voltage Design

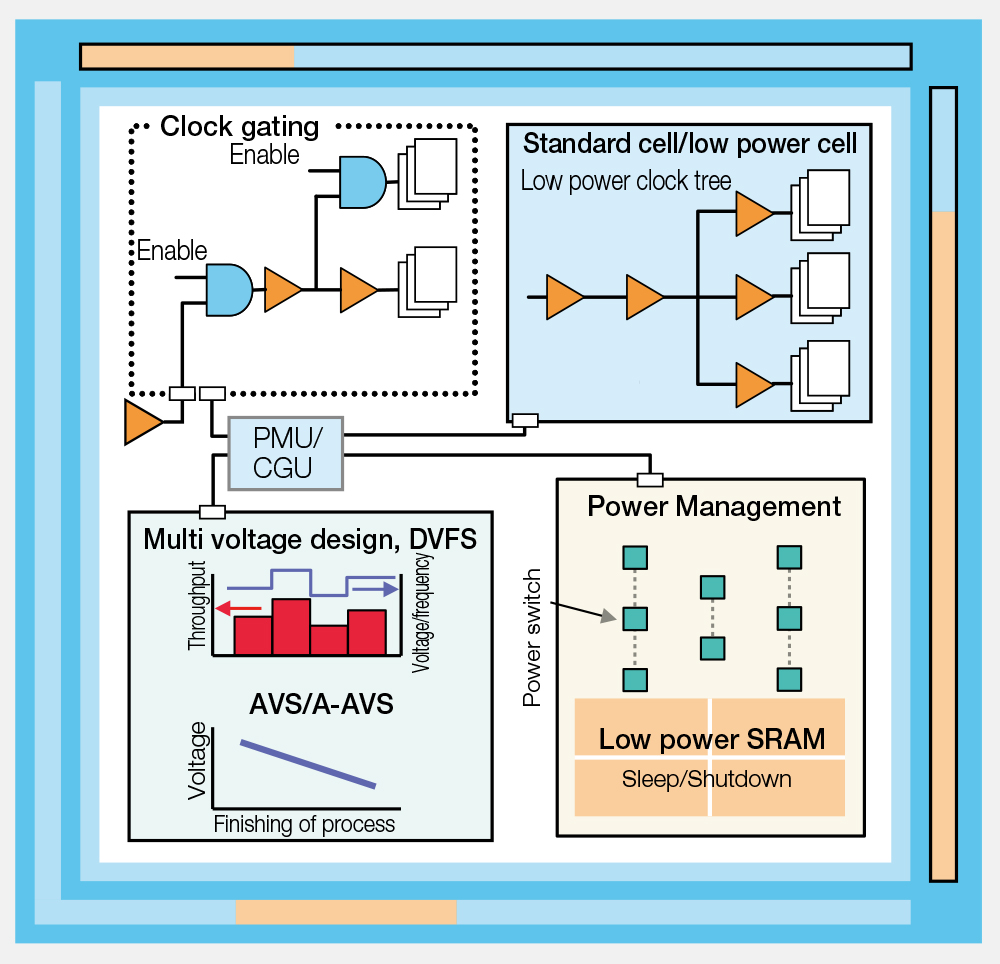

This technology involves supplying different voltages to an LSI (Large-Scale Integration) to reduce power consumption during circuit block operation. A high voltage is supplied for high-speed operation circuit blocks, while a low voltage is provided for low-speed operation circuit blocks. By utilizing UPF/CPF (Unified Power Format/Common Power Format), physical design and verification of circuit blocks with varying voltages can be performed concurrently. This approach minimizes the extension of the development period for low-power consumption design.

Clock Gating

Clock gating enables the power consumption of LSIs during operation to be reduced by stopping the supply of clock signals to circuit blocks that do not need to operate.

Power Management

We provide power management technology to control power gating, SRAM sleep, and shut-down mode in a comprehensive manner. By thoroughly eliminating waste, this technology contributes to low power consumption. With its unique power switch controlling system, Socionext's power management technology suppresses the rush current noise generated when the power supply is turned on and off to prevent LSIs from malfunctioning. In addition, using UPF/CPF allows physical design and verification of circuit blocks that have a power shutdown circuit to be performed together, minimizing extension of the development period.

Adaptive Power supply Control(DVFS*1, AVS*2/Advanced-AVS)

We can use DVFS, which is for varying the voltage and frequency according to the required throughput. This technology also adaptively determines the operating voltage according to voltage variation due to manufacturing variability and operates the LSI at the lowest voltage at which its operation is guaranteed, leading to reduced power consumption of the LSI during both operation and standby.

*1:DVFS(Dynamic Voltage Frequency Scaling)

*2:AVS(Adaptive Voltage Scaling)

Standard Cell

In the area of advanced technology, in addition to the standard cell area, routability contributes to the low power consumption of LSIs. We provide our original standard cell that is far superior to that of other companies. In addition, we offer a rich line-up of cells that are effective for achieving low power consumption of the clock system.

Low power SRAM

An LSI with high-capacity SRAM may have a problem with the power consumption of the SRAM macro. In such cases, power consumption may be reduced by using a multi-mode SRAM. Multi-mode SRAM features a standby mode, sleep mode, and shut-down mode, as well as a normal operation mode.

The standby mode allows for the operating power of an SRAM macro to be 0 by stopping the clock operation inside the macro. In sleep mode, leakage power is reduced by deactivating peripheral circuits of the SRAM macro. Power can only be shut down with an SRAM in shutdown mode. The optimization of the SRAM configuration to be used contributes to low power consumption as well. We help customers select the best SRAM from the logic design phase.

| Operating Mode | Function | Effect |

|---|---|---|

| Normal | To operate RAM normally | - |

| Standby | To stop the SRAM operation | The operating power is 0 |

| Sleep | To retain data | Leakage power is reduced to one-third* |

| Shutdown | To shut down the power with only the SRAM | Leakage power is reduced to one-sixth* |

*: Depends on the SRAM structure

Low Power Design Environment that Fully adopts UPF/CPF

Socionext offers a total solution that supports power gating, multi-power supply, and multi-voltage design through consistent power supply specification management with UPF*1 and CPF*2, RTL simulation for complicated power supply design due to an increased number of integrated IPs, multi-power supply verification, and physical design.

*1:UPF (Unified Power Format) is a standard specification that defines the Low power design guidelines standardized by IEEE Std. 1801 (http://www.ieee.org/)

*2:CPF (Common Power Format) is a standard specification that defines the Low power design guidelines standardized as Si2 (http://www.si2.org/?page=811)